EPF10K50S

Key Features

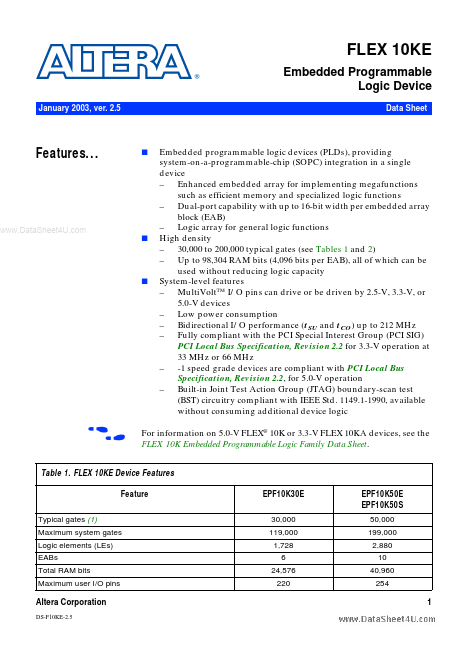

- Embedded programmable logic devices (PLDs), providing system-on-a-programmable-chip (SOPC) integration in a single device - Enhanced embedded array for implementing megafunctions such as efficient memory and specialized logic functions - Dual-port capability with up to 16-bit width per embedded array block (EAB) - Logic array for general logic functions High density - 30,000 to 200,000 typical gates (see Tables 1 and 2) - Up to 98,304 RAM bits (4,096 bits per EAB), all of which can be used without reducing logic capacity System-level features - MultiVoltTM I/O pins can drive or be driven by 2.5-V, 3.3-V, or 5.0-V devices - Low power consumption - Bidirectional I/O performance (tSU and tCO) up to 212 MHz - Fully compliant with the PCI Special Interest Group (PCI SIG) PCI Local Bus Specification, Revision 2.2 for 3.3-V operation at 33 MHz or 66 MHz - -1 speed grade devices are compliant with PCI Local Bus Specification, Revision 2.2, for 5.0-V operation - Built-in Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry compliant with IEEE Std. 1149.1-1990, available without consuming additional device logic f For information on 5.0-V FLEX® 10K or 3.3-V FLEX 10KA devices, see the FLEX 10K Embedded Programmable Logic Family Data Sheet. Table

- FLEX 10KE Device Features Feature Typical gates (1) Maximum system gates Logic elements (LEs) EABs Total RAM bits Maximum user I/O pins Altera Corporation