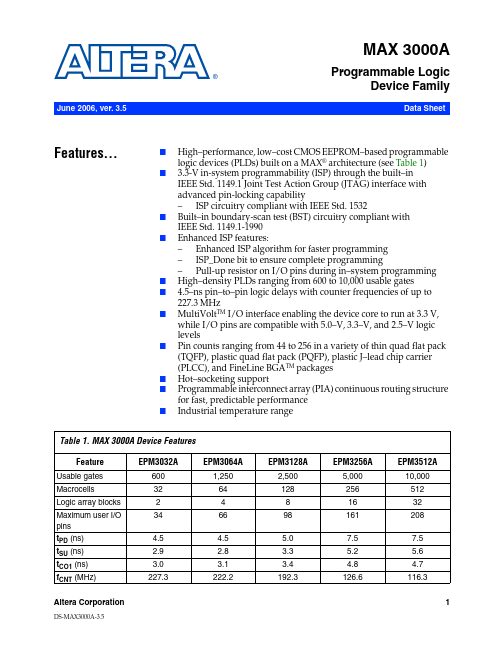

| Part | EPM3064A |

|---|---|

| Description | Programmable Logic |

| Manufacturer | Altera |

| Size | 729.56 KB |

Pricing from 46.2 USD, available from Verical and element14 APAC.Powered by Octopart

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Verical | 19520 | 160+ : 46.2 USD | View Offer |

| element14 APAC | 0 | 1+ : 9.76 SGD 10+ : 8.55 SGD 25+ : 7.08 SGD 50+ : 6.17 SGD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| GL3510-52 | Genesys Logic | USB 3.1 Gen 1 Hub Controller |

| MAC97A6 | KCD | 0.8A Logic level TRIAC |

| CS43198 | Cirrus Logic | 32-Bit High-Performance DAC |