EPM5128 Overview

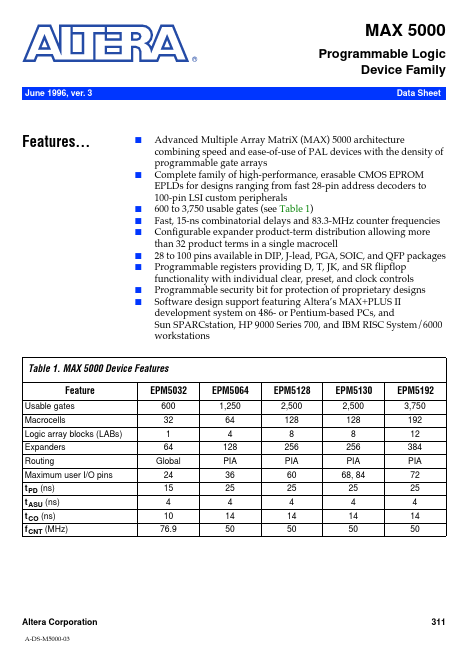

Key Specifications

Description

s Programming support with Altera’s Master Programming Unit (MPU) or programming hardware from other manufacturers s Additional design entry and simulation support provided by EDIF, LPM, Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as Cadence, Data I/O, Exemplar, Mentor Graphics, MINC, OrCAD, Synopsys, VeriBest, and Viewlogic The MAX 5000 family combines innovative a.