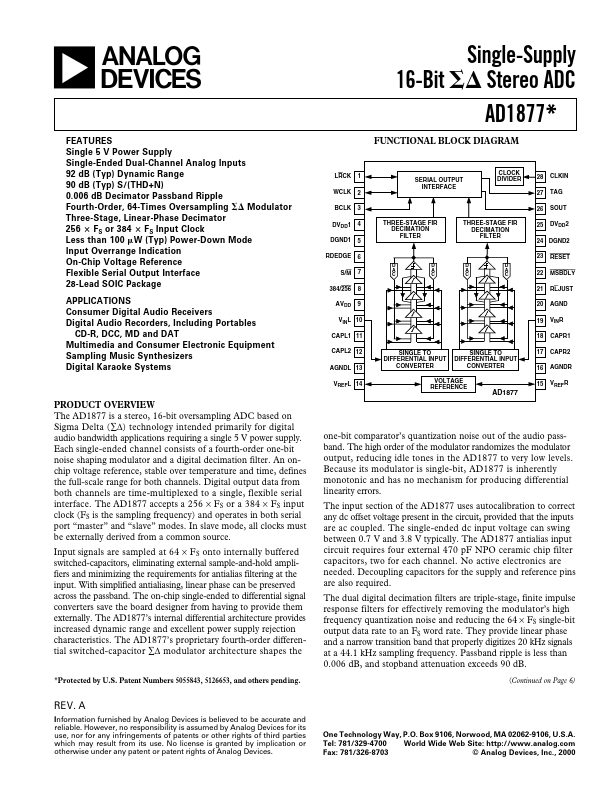

| Part | AD1877 |

|---|---|

| Description | Single-Supply 16-Bit Stereo ADC |

| Manufacturer | Analog Devices |

| Size | 253.49 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| ADS1115 | Texas Instruments | 16-Bit ADC |

| ES7210 | Everest Semiconductor | High Performance Four Channels Audio ADC |

| PCM1808 | Texas Instruments | 96-kHz Stereo ADC |