AD1959

FEATURES

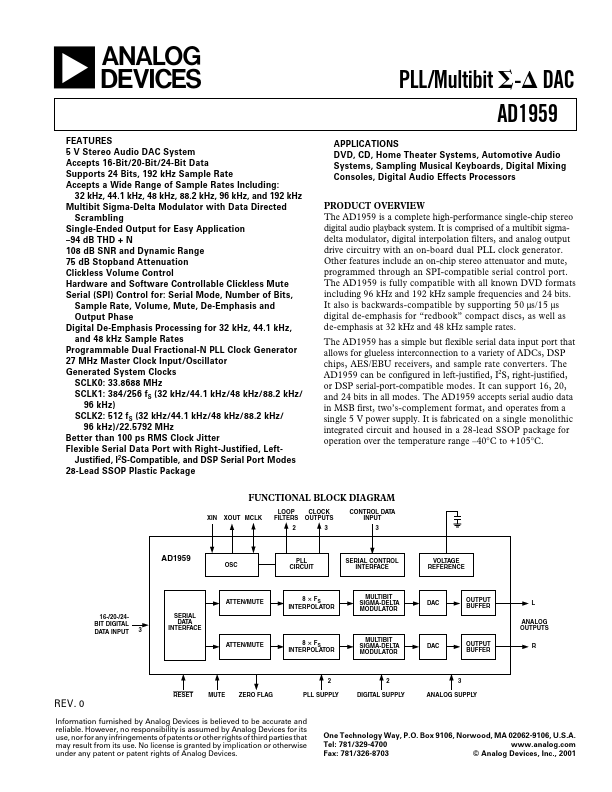

5 V Stereo Audio DAC System Accepts 16-Bit/20-Bit/24-Bit Data Supports 24 Bits, 192 k Hz Sample Rate Accepts a Wide Range of Sample Rates Including: 32 k Hz, 44.1 k Hz, 48 k Hz, 88.2 k Hz, 96 k Hz, and 192 k Hz Multibit Sigma-Delta Modulator with Data Directed Scrambling Single-Ended Output for Easy Application

- 94 d B THD + N 108 d B SNR and Dynamic Range 75 d B Stopband Attenuation Clickless Volume Control Hardware and Software Controllable Clickless Mute Serial (SPI) Control for: Serial Mode, Number of Bits, Sample Rate, Volume, Mute, De-Emphasis and Output Phase Digital De-Emphasis Processing for 32 k Hz, 44.1 k Hz, and 48 k Hz Sample Rates Programmable Dual Fractional-N PLL Clock Generator 27 MHz Master Clock Input/Oscillator Generated System Clocks SCLK0: 33.8688 MHz SCLK1: 384/256 f S (32 k Hz/44.1 k Hz/48 k Hz/88.2 k Hz/ 96 k Hz) SCLK2: 512 f S (32 k Hz/44.1 k Hz/48 k Hz/88.2 k Hz/ 96 k Hz)/22.5792 MHz Better than 100 ps RMS Clock Jitter Flexible Serial Data Port with Right-Justified, Left...