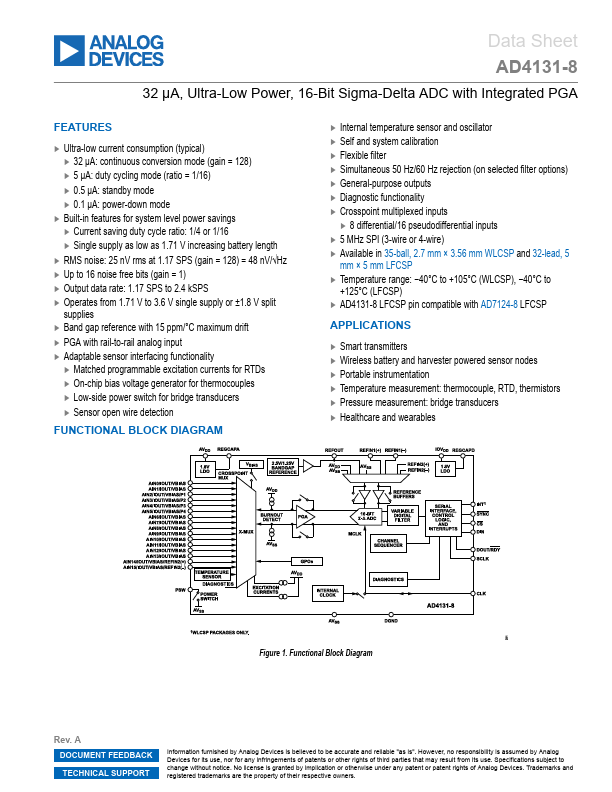

AD4131-8 Overview

Key Specifications

Key Features

- Ultra-low current consumption (typical)

- 32 µA: continuous conversion mode (gain =

- 5 µA: duty cycling mode (ratio = 1/16)

- 0.5 µA: standby mode

- 0.1 µA: power-down mode

- Built-in features for system level power savings

- Current saving duty cycle ratio: 1/4 or 1/16

- Single supply as low as 1.71 V increasing battery length

- RMS noise: 25 nV rms at 1.17 SPS (gain =

- Up to 16 noise free bits (gain =