AD5371

FEATURES

40-channel DAC in 80 Lead LQFP and 100 Ball CSPBGA Guaranteed monotonic to 14 bits Maximum output voltage span of 4 × VREF (20 V) Nominal output voltage range of -4 V to +8 V Multiple, Independent output spans available System calibration function allowing user-programmable offset and gain Channel grouping and addressing features

Thermal Monitor Function DSP/microcontroller-patible serial interface LVDS serial interface 2.5 V to 5.5 V JEDEC-pliant digital levels

DVCC VDD VSS AGND DNGD

40-Channel, 14-Bit Serial Input, Voltage-Output DAC AD5371

Power-on reset Digital reset (RESET) Clear function to user-defined SIGGND (CLR pin) Simultaneous update of DAC outputs (LDAC pin)

APPLICATIONS

Level setting in automatic test equipment (ATE) Variable optical attenuators (VOA) Optical switches Industrial control systems Instrumentation

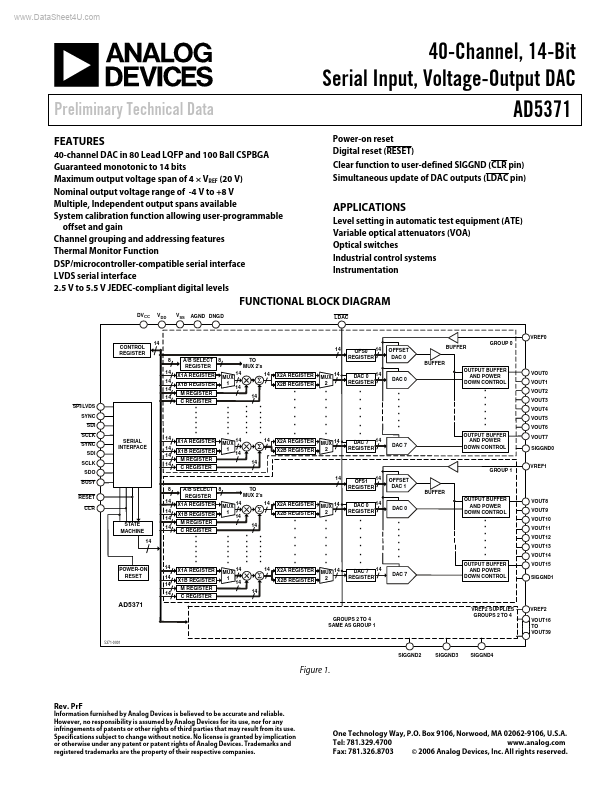

FUNCTIONAL BLOCK DIAGRAM

LDAC

VREF0 CONTROL REGISTER 14 14 8 14 14 14 14 SPI/LVDS SYNC SDI SCLK SYNC SDI SCLK SDO BUSY 8 RESET CLR STATE MACHINE 14 14...