AD7172-4

AD7172-4 is Sigma-Delta ADC manufactured by Analog Devices.

FEATURES

GENERAL DESCRIPTION

Fast and flexible output rate: 1.25 SPS to 31.25 k SPS Channel scan data rate of 6.21 k SPS/channel (161 μs settling) Performance specifications

17.2 noise free bits at 31.25 k SPS 24 noise free bits at 5 SPS INL: ±2 ppm of FSR 85 d B rejection of 50 Hz and 60 Hz with 50 ms settling User configurable input channels 4 fully differential channels or 8 single-ended channels Crosspoint multiplexer True rail-to-rail analog and reference input buffers Internal or external clock Power supply AVDD1 = 3.0 V to 5.5 V, AVDD2 = IOVDD = 2 V to 5.5 V Split supply with AVDD1 and AVSS at ±2.5 V or ±1.65 V ADC current: 1.5 m A Temperature range:

- 40°C to +105°C 3- or 4-wire serial digital interface (Schmitt trigger on SCLK) Serial port interface (SPI), QSPI-, MICROWIRE-, and DSP- patible

APPLICATIONS

Process control: PLC/DCS modules Temperature and pressure measurement

Medical and scientific multichannel instrumentation Chromatography

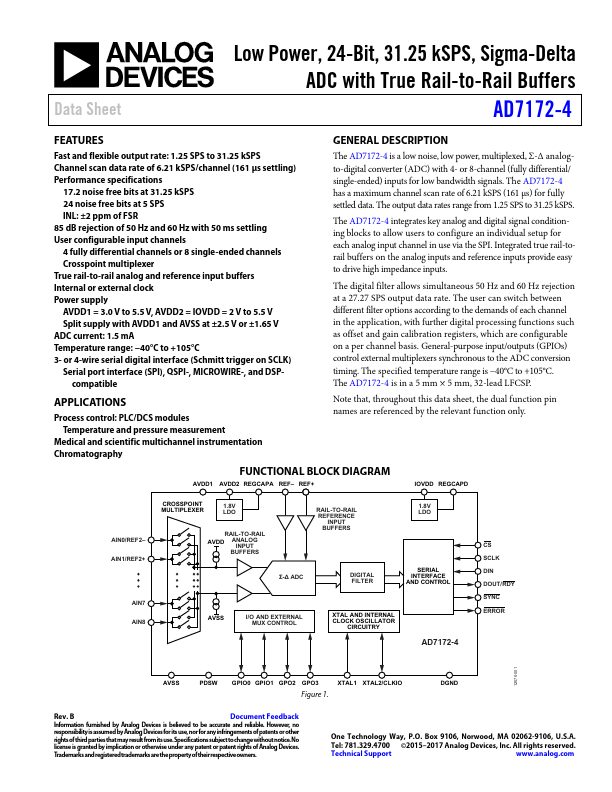

The AD7172-4 is a low noise, low power, multiplexed, Σ-Δ analogto-digital converter (ADC) with 4- or 8-channel (fully differential/ single-ended) inputs for low bandwidth signals. The AD7172-4 has a maximum channel scan rate of 6.21 k SPS (161 μs) for fully settled data. The output data rates range from 1.25 SPS to 31.25 k SPS.

The AD7172-4 integrates key analog and digital signal conditioning blocks to allow users to configure an individual setup for each analog input channel in use via the SPI. Integrated true rail-torail buffers on the analog inputs and reference inputs provide easy to drive high impedance inputs.

The digital filter allows simultaneous 50 Hz and 60 Hz rejection at a 27.27 SPS output data rate. The user can switch between different filter options according to the demands of each channel in the application, with further digital processing functions such as offset and gain calibration registers, which are configurable on a per channel basis. General-purpose input/outputs (GPIOs) control external multiplexers...