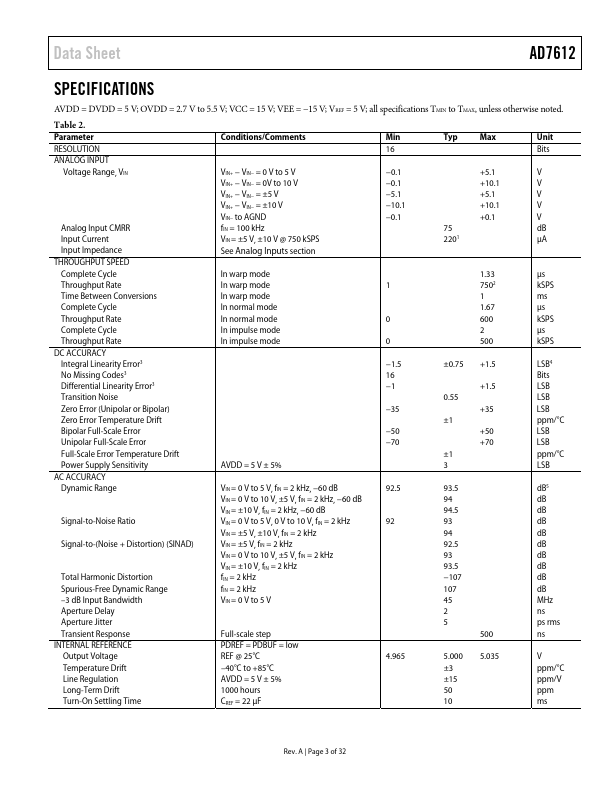

Datasheet Summary

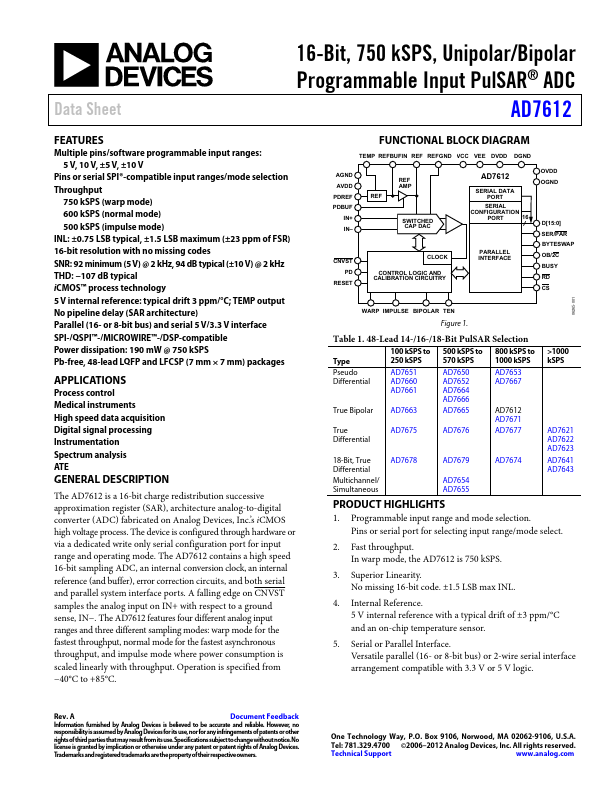

16-Bit, 750 kSPS, Unipolar/Bipolar Programmable Input PulSAR® ADC AD7612

Features

Multiple pins/software programmable input ranges: 5 V, 10 V, ±5 V, ±10 V Pins or serial SPI®-patible input ranges/mode selection Throughput 750 kSPS (warp mode) 600 kSPS (normal mode) 500 kSPS (impulse mode) INL: ±0.75 LSB typical, ±1.5 LSB maximum (±23 ppm of FSR) 16-bit resolution with no missing codes SNR: 92 minimum (5 V) @ 2 kHz, 94 dB typical (±10 V) @ 2 kHz THD:

- 107 dB typical iCMOS™ process technology 5 V internal reference: typical drift 3 ppm/°C; TEMP output No pipeline delay (SAR architecture) Parallel (16- or 8-bit bus) and serial 5 V/3.3 V interface SPI-/QSPI™-/MICROWIRE™-/DSP-patible...