Datasheet Summary

3 V/5 V, ±10 V Input Range, 1 mW 3-Channel 16-Bit, Sigma-Delta ADC

Features

Charge balancing ADC 16 bits, no missing codes ±0.003% nonlinearity

High level (±10 V) and low level (±10 mV) input channels True bipolar ±100 mV capability on low level input

Channels without requiring charge pumps Programmable gain front end

Gains from 1 to 128 3-wire serial interface

SPI, QSPI™, MICROWIRE™ and DSP patible Schmitt trigger input on SCLK Ability to buffer the analog input 2.7 V to 3.3 V or 4.75 V to 5.25 V operation Power dissipation 1 mW at 3 V Standby current 8 μA maximum 20-lead SOIC and TSSOP packages

GENERAL DESCRIPTION

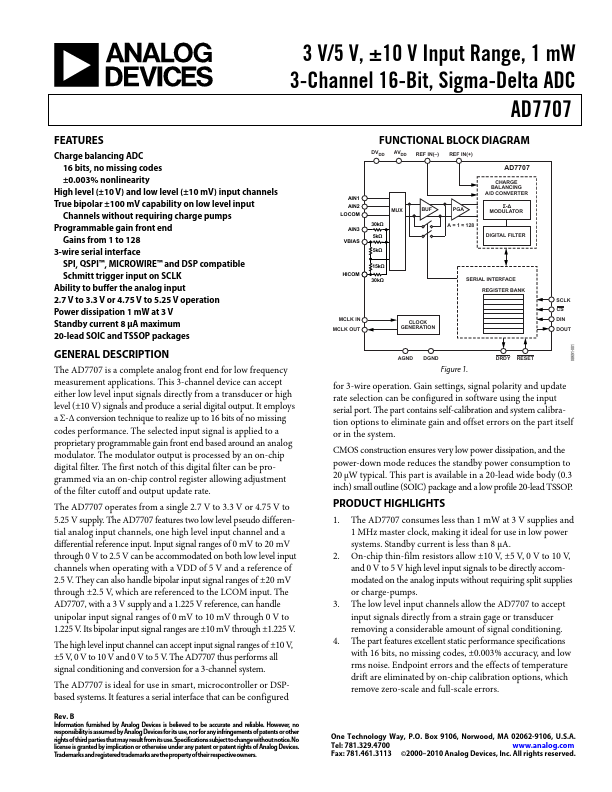

The AD7707 is a plete analog front end for low frequency...