AD9139

Overview

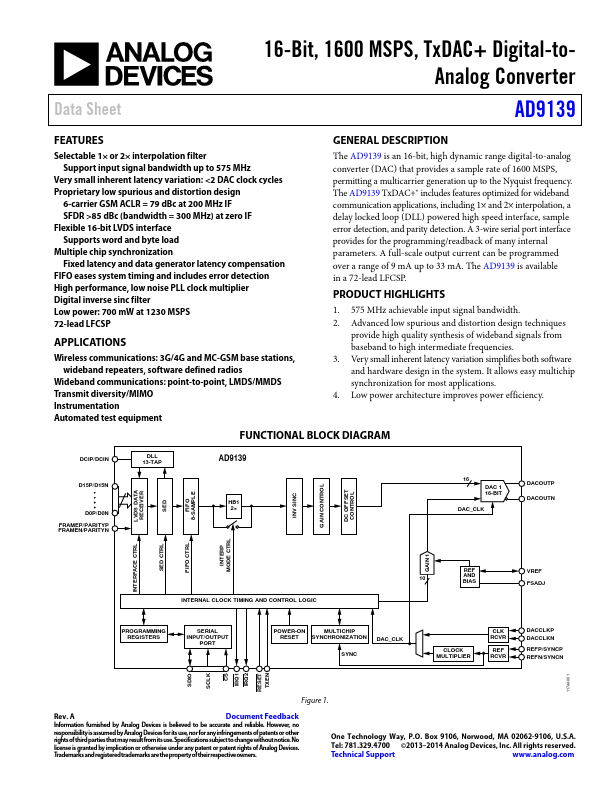

Selectable 1× or 2× interpolation filter Support input signal bandwidth up to 575 MHz Very small inherent latency variation: <2 DAC clock cycles Proprietary low spurious and distortion design 6-carrier GSM ACLR = 79 dBc at 200 MHz IF SFDR >85 dBc (bandwidth = 300 MHz) at zero IF Flexible 16-bit LVDS interface Supports word and byte load Multiple chip synchronization Fixed latency and data generator latency compensation FIFO eases system timing and includes error detection High performance, low noise PLL clock multiplier Digital inverse sinc filter Low power: 700 mW at 1230 MSPS 72-lead LFCSP.