AD9212

AD9212 is Serial LVDS A/D Converter manufactured by Analog Devices.

Data Sheet

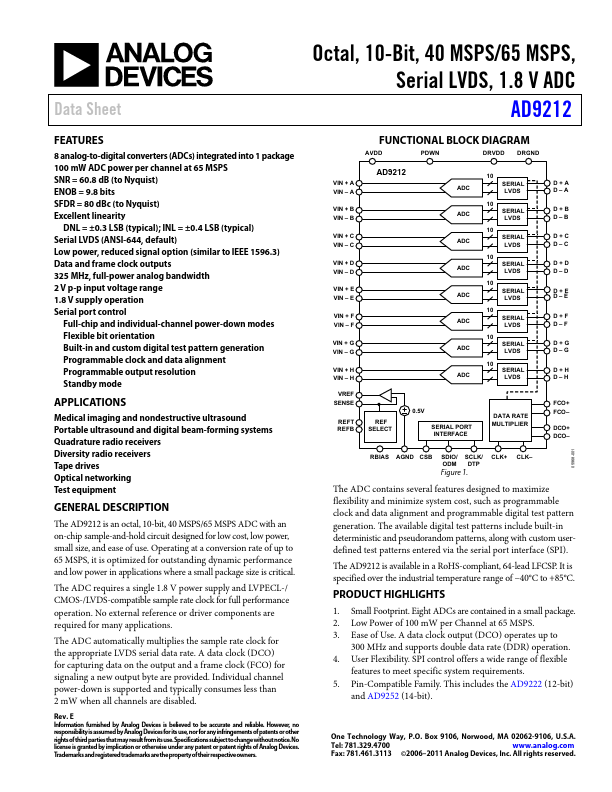

Octal, 10-Bit, 40 MSPS/65 MSPS, Serial LVDS, 1.8 V ADC AD9212

Features

8 analog-to-digital converters (ADCs) integrated into 1 package 100 mW ADC power per channel at 65 MSPS SNR = 60.8 dB (to Nyquist) ENOB = 9.8 bits SFDR = 80 dBc (to Nyquist) Excellent linearity

DNL = ±0.3 LSB (typical); INL = ±0.4 LSB (typical) Serial LVDS (ANSI-644, default) Low power, reduced signal option (similar to IEEE 1596.3) Data and frame clock outputs 325 MHz, full-power analog bandwidth 2 V p-p input voltage range 1.8 V supply operation Serial port control

Full-chip and individual-channel power-down modes Flexible bit orientation Built-in and custom digital test pattern generation Programmable...