Datasheet Summary

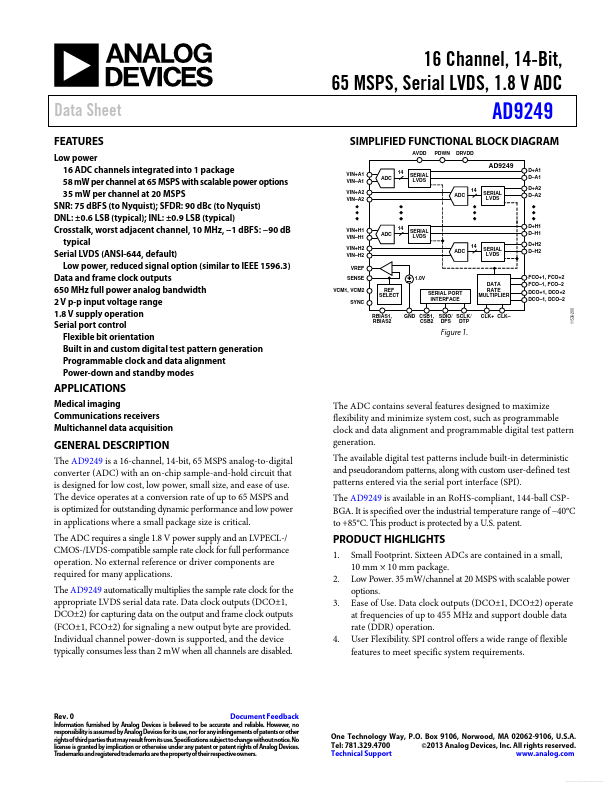

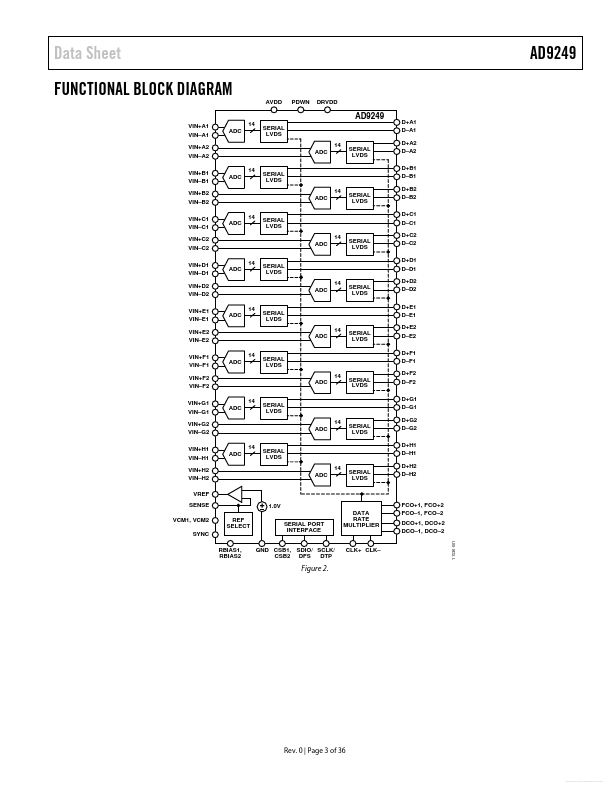

16 Channel, 14-Bit, 65 MSPS, Serial LVDS, 1.8 V ADC

Data Sheet

Features

Low power 16 ADC channels integrated into 1 package 58 mW per channel at 65 MSPS with scalable power options 35 mW per channel at 20 MSPS SNR: 75 dBFS (to Nyquist); SFDR: 90 dBc (to Nyquist) DNL: ±0.6 LSB (typical); INL: ±0.9 LSB (typical) Crosstalk, worst adjacent channel, 10 MHz,

- 1 dBFS:

- 90 dB typical Serial LVDS (ANSI-644, default) Low power, reduced signal option (similar to IEEE 1596.3) Data and frame clock outputs 650 MHz full power analog bandwidth 2 V p-p input voltage range 1.8 V supply operation Serial port control Flexible bit orientation Built in and custom digital test pattern generation Programmable...