AD9262

Description

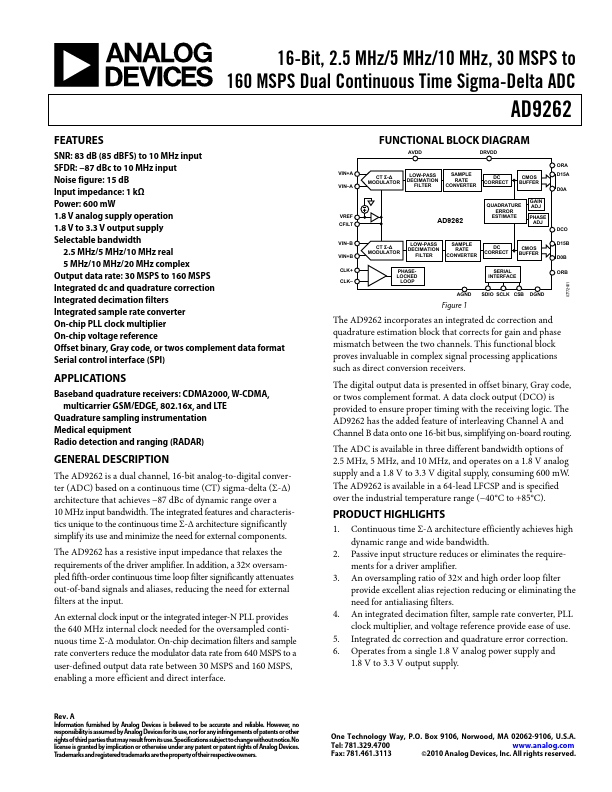

The AD9262 is a dual channel, 16-bit analog-to-digital converter (ADC) based on a continuous time (CT) sigma-delta (Σ-Δ) architecture that.

Key Features

- 5 MHz/5 MHz/10 MHz real 5 MHz/10 MHz/20 MHz complex Output data rate: 30 MSPS to 160 MSPS Integrated dc and quadrature correction Integrated decimation filters Integrated sample rate converter On-chip PLL clock multiplier On-chip voltage reference Offset binary, Gray code, or twos complement data format Serial control interface (SPI)