AD9446

FEATURES

100 MSPS guaranteed sampling rate 100 d B two-tone SFDR with 30 MHz and 31 MHz 81.6 d B SNR with 30 MHz input (3.2 V p-p input, 80Msps) 90 d Bc SFDR with30 MHz input (3.2 V p-p input, 80Msps) Excellent linearity DNL = ±0.5 LSB typical INL = ±3.0 LSB typical 2.3 W power dissipation 3.3 V and 5 V supply operation 2.0 V p-p to 3.2 V p-p differential full-scale input LVDS outputs (ANSI-644 patible) or CMOS outputs Data format select (offset binary or twos pliment) Output clock available

16-Bit, 80/100 MSPS, A/D Converter AD9446

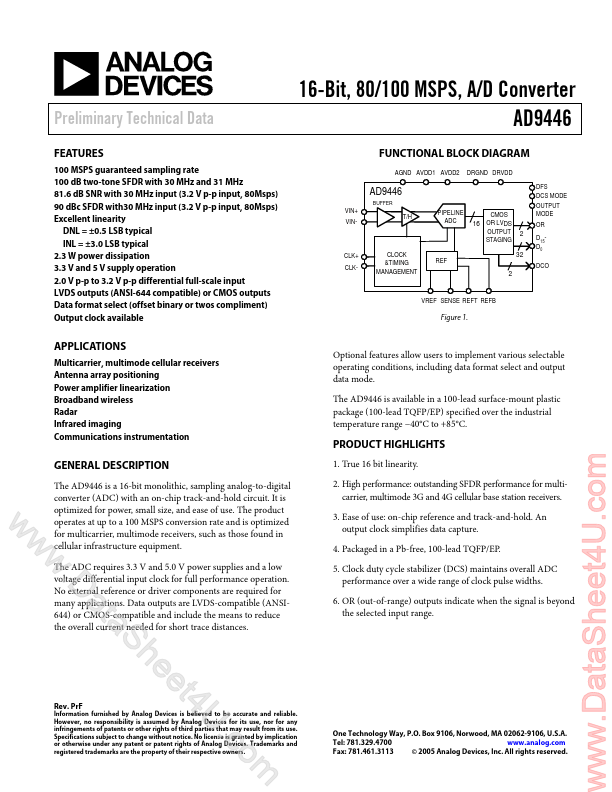

FUNCTIONAL BLOCK DIAGRAM

AGND AVDD1 AVDD2 DRGND DRVDD DFS DCS MODE OUTPUT MODE

VIN+ VINBUFFER

T/H

PIPELINE ADC

16 OR LVDS

CMOS

OUTPUT STAGING

2 32

OR D15D0 DCO

CLK+ CLK-

CLOCK &TIMING MANAGEMENT

VREF SENSE REFT REFB

Figure 1.

APPLICATIONS

Multicarrier, multimode cellular receivers Antenna array positioning Power amplifier linearization Broadband wireless Radar Infrared imaging munications instrumentation

Optional features allow...