AD9508

Key Features

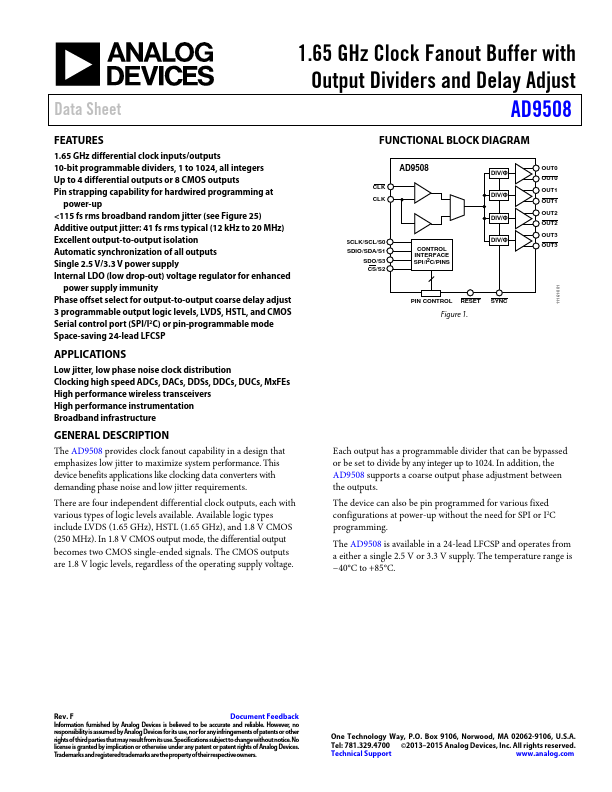

- 65 GHz differential clock inputs/outputs 10-bit programmable dividers, 1 to 1024, all integers Up to 4 differential outputs or 8 CMOS outputs Pin strapping capability for hardwired programming at power-up <115 fs rms broadband random jitter (see Figure 25) Additive output jitter: 41 fs rms typical (12 kHz to 20 MHz) Excellent output-to-output isolation Automatic synchronization of all outputs Single 2.5 V/3.3 V power supply Internal LDO (low drop-out) voltage regulator for enhanced power supply immunity Phase offset select for output-to-output coarse delay adjust 3 programmable output logic levels, LVDS, HSTL, and CMOS Serial control port (SPI/I2C) or pin-programmable mode Space-saving 24-lead LFCSP