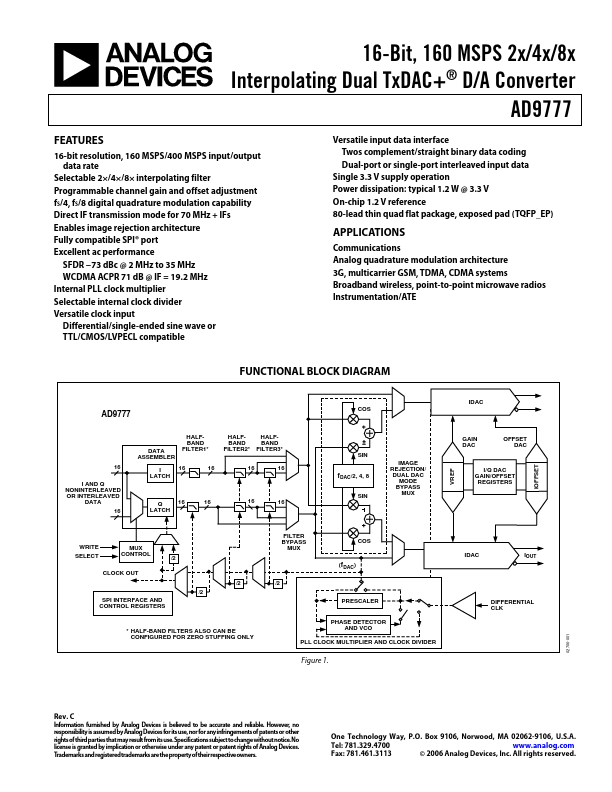

AD9777

FEATURES

16-bit resolution, 160 MSPS/400 MSPS input/output data rate

Selectable 2×/4×/8× interpolating filter Programmable channel gain and offset adjustment f S/4, f S/8 digital quadrature modulation capability Direct IF transmission mode for 70 MHz + IFs Enables image rejection architecture Fully patible SPI® port Excellent ac performance

SFDR

- 73 d Bc @ 2 MHz to 35 MHz WCDMA ACPR 71 d B @ IF = 19.2 MHz Internal PLL clock multiplier Selectable internal clock divider Versatile clock input Differential/single-ended sine wave or TTL/CMOS/LVPECL patible

Versatile input data interface Twos plement/straight binary data coding Dual-port or single-port interleaved input data

Single 3.3 V supply operation Power dissipation: typical 1.2 W @ 3.3 V On-chip 1.2 V reference 80-lead thin quad flat package, exposed pad (TQFP_EP)

APPLICATIONS munications Analog quadrature modulation architecture 3G,...