ADCMP562

FEATURES

Differential PECL patible outputs 700 ps propagation delay input to output 75 ps propagation delay dispersion Input mon-mode range:

- 2.0 V to +3.0 V Robust input protection Differential latch control Internal latch pull-up resistors Power supply rejection greater than 85 d B 700 ps minimum pulse width 1.5 GHz equivalent input rise time bandwidth Typical output rise/fall time of 500 ps ESD protection > 4k V HBM, >200V MM Programmable hysteresis

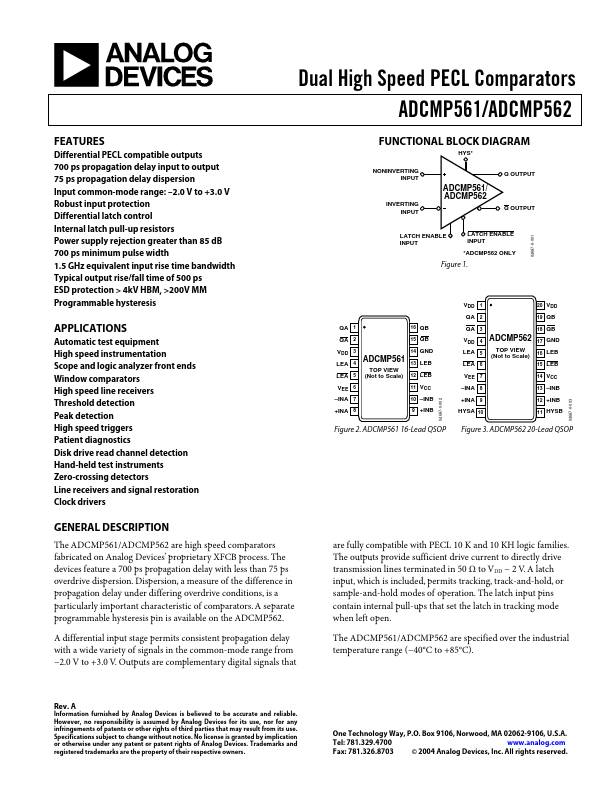

FUNCTIONAL BLOCK DIAGRAM

HYS- NONINVERTING INPUT Q OUTPUT

ADCMP561/ ADCMP562

INVERTING INPUT Q OUTPUT

- ADCMP562 ONLY

Figure 1.

VDD 1 QA 2

04687-0-001

LATCH ENABLE INPUT

LATCH ENABLE INPUT

20 VDD 19 QB 18 QB

APPLICATIONS

Automatic test equipment High speed instrumentation Scope and logic analyzer front ends Window parators High speed line receivers Threshold detection Peak detection High speed triggers Patient diagnostics Disk drive read channel detection Hand-held test instruments Zero-crossing detectors Line receivers and...