ADF4193

ADF4193 is Fast Settling PLL Frequency Synthesizer manufactured by Analog Devices.

Data Sheet

Low Phase Noise, Fast Settling PLL Frequency Synthesizer ADF4193

Features

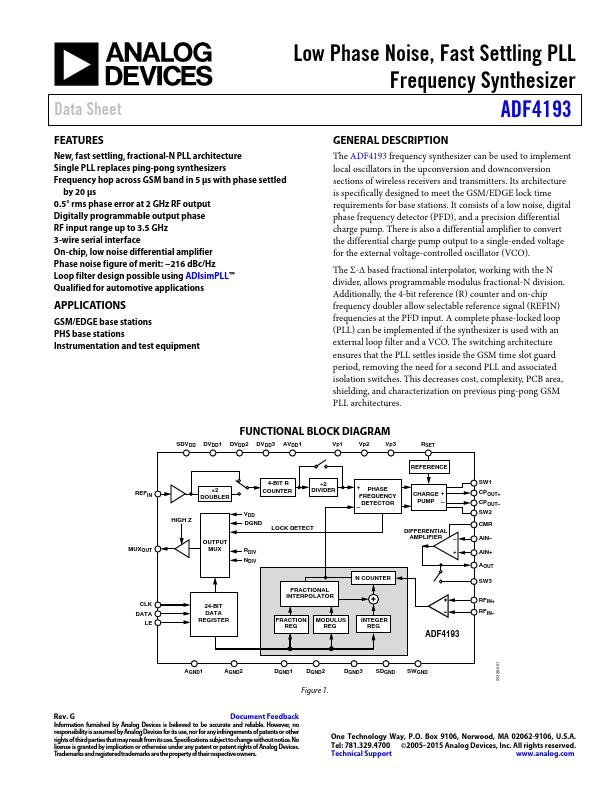

New, fast settling, fractional-N PLL architecture Single PLL replaces ping-pong synthesizers Frequency hop across GSM band in 5 µs with phase settled by 20 µs 0.5° rms phase error at 2 GHz RF output Digitally programmable output phase RF input range up to 3.5 GHz 3-wire serial interface On-chip, low noise differential amplifier Phase noise figure of merit:

- 216 dBc/Hz Loop filter design possible using ADIsimPLL™ Qualified for automotive applications

APPLICATIONS

GSM/EDGE base stations PHS base stations Instrumentation and test equipment

GENERAL DESCRIPTION

The ADF4193 frequency synthesizer can be used...