ADF4377

Overview

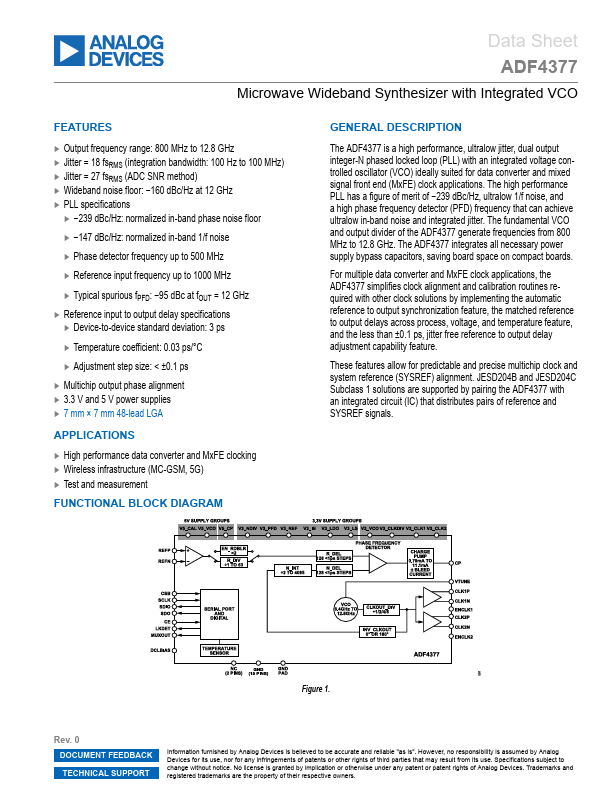

The ADF4377 is a high performance, ultralow jitter, dual output integer-N phased locked loop (PLL) with an integrated voltage controlled oscillator (VCO) ideally suited for data converter and mixed signal front end (MxFE) clock applications. The high performance PLL has a.

- Output frequency range: 800 MHz to 12.8 GHz

- Jitter = 18 fsRMS (integration bandwidth: 100 Hz to 100 MHz)

- Jitter = 27 fsRMS (ADC SNR method)

- Wideband noise floor: -160 dBc/Hz at 12 GHz

- PLL specifications

- -239 dBc/Hz: normalized in-band phase noise floor

- -147 dBc/Hz: normalized in-band 1/f noise

- Phase detector frequency up to 500 MHz

- Reference input frequency up to 1000 MHz

- Typical spurious fPFD: -95 dBc at fOUT = 12 GHz