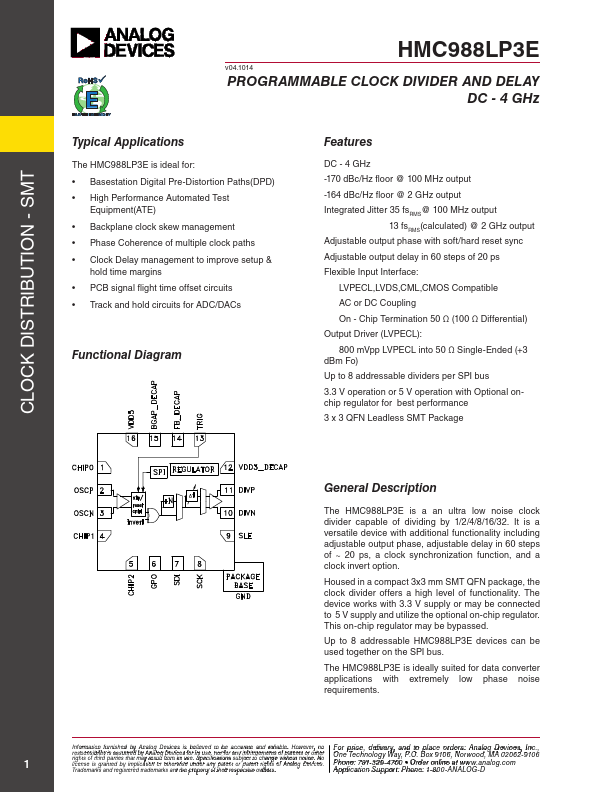

HMC988LP3E

Features

- 4 GHz -170 d Bc/Hz floor @ 100 MHz output -164 d Bc/Hz floor @ 2 GHz output Integrated Jitter 35 fs RMS@ 100 MHz output

13 fs RMS(calculated) @ 2 GHz output Adjustable output phase with soft/hard reset sync Adjustable output delay in 60 steps of 20 ps Flexible Input Interface:

LVPECL,LVDS,CML,CMOS patible AC or DC Coupling On

- Chip Termination 50 Ω (100 Ω Differential) Output Driver (LVPECL): 800 m Vpp LVPECL into 50 Ω Single-Ended (+3 d Bm Fo) Up to 8 addressable dividers per SPI bus 3.3 V operation or 5 V operation with Optional onchip regulator for best performance 3 x 3 QFN Leadless SMT Package

General Description

The HMC988LP3E is a an ultra low noise clock divider capable of dividing by 1/2/4/8/16/32. It is a versatile device with additional functionality including adjustable output phase, adjustable delay in 60 steps of ~ 20 ps, a clock synchronization function, and a clock invert option.

Housed in a pact 3x3 mm SMT QFN package, the clock divider offers a high level...