AD9516-5 Description

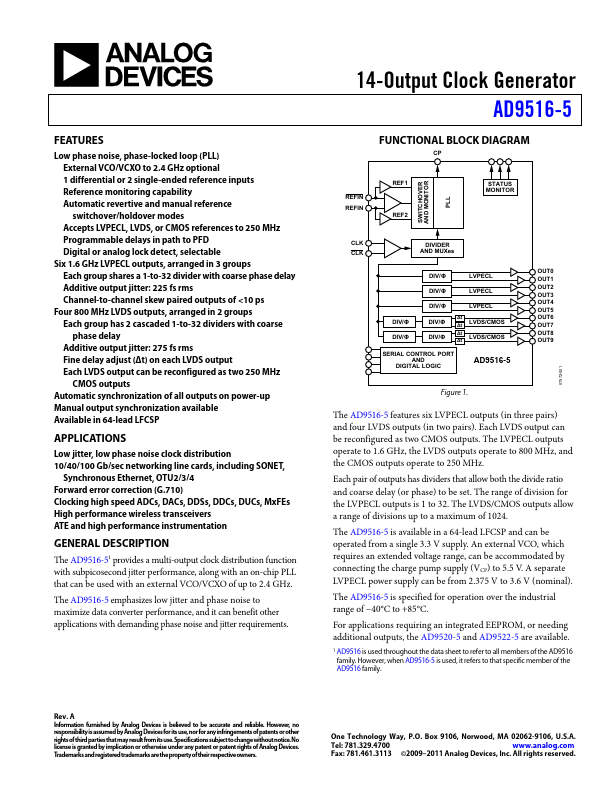

FEATURES Low phase noise, phase-locked loop (PLL) External VCO/VCXO to 2.4 GHz optional 1 differential or 2 single-ended reference inputs Reference monitoring capability Automatic revertive and manual reference switchover/holdover modes Accepts LVPECL, LVDS, or CMOS references to 250 MHz Programmable delays in path to PFD Digital or analog lock detect, selectable Six 1.6 GHz LVPECL outputs, arranged in 3 groups Each...