ADF4382A Description

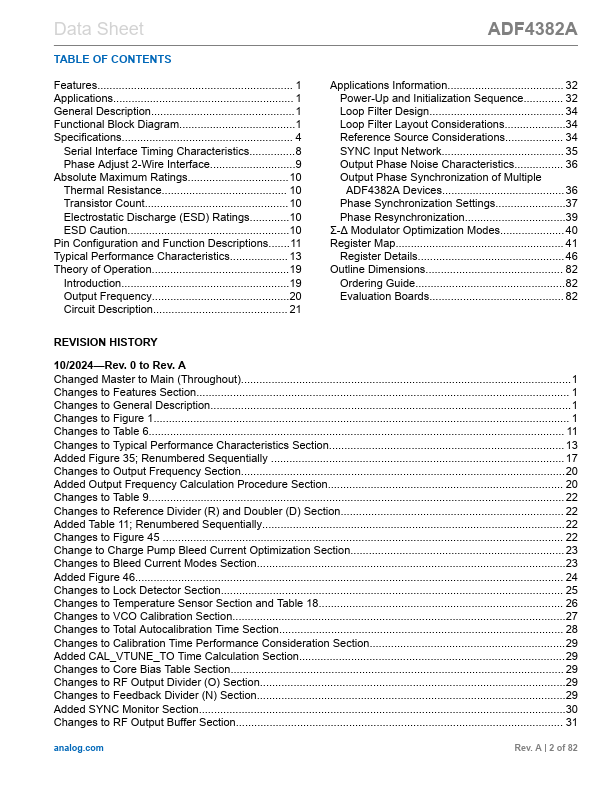

The ADF4382A is a high performance, ultra-low jitter, fractional-N phased-locked loop (PLL) with an integrated voltage controlled oscillator (VCO) ideally suited for local oscillator (LO) generation for 5G applications or data converter clock applications. The high performance PLL has a figure of merit of −239 dBc/Hz, low 1/f noise and high PFD frequency of 625 MHz in integer mode that can achieve ultra-low in-band...

ADF4382A Key Features

- Fundamental output frequency range: 11.5 GHz to 21 GHz

- Divide by 2 output frequency range: 5.75 GHz to 10.5 GHz

- Divide by 4 output frequency range: 2.875 GHz to 5.25 GHz

- Integrated RMS jitter at 20 GHz = 20 fs (integration bandwidth

- Integrated RMS jitter at 20 GHz = 31 fs (ADC SNR method)

- VCO fast calibration time < 1 μs

- VCO autocalibration time < 100 μs

- Phase noise floor: -156 dBc/Hz at 20 GHz

- PLL specifications

- 239 dBc/Hz: normalized in-band phase noise floor