AT5C1008

AT5C1008 is 128K x 8 Static RAM manufactured by Anloy Technologies.

Features

» Operating Temperature range of +125°C to -55°C » Access times of: 12, 15, 20, 25, 30, 35, 45, 55 and 70 ns » Battery Backup: 2V data retention » Fast output enable (t AOE) for cache applications » Low standby power » Fully static operation, no clock or refresh required » TTL patible Inputs and Outputs » Easy memory expansion with CE1, CE2, and OE options. » Single +5V power supply

128K x 8 Static RAM

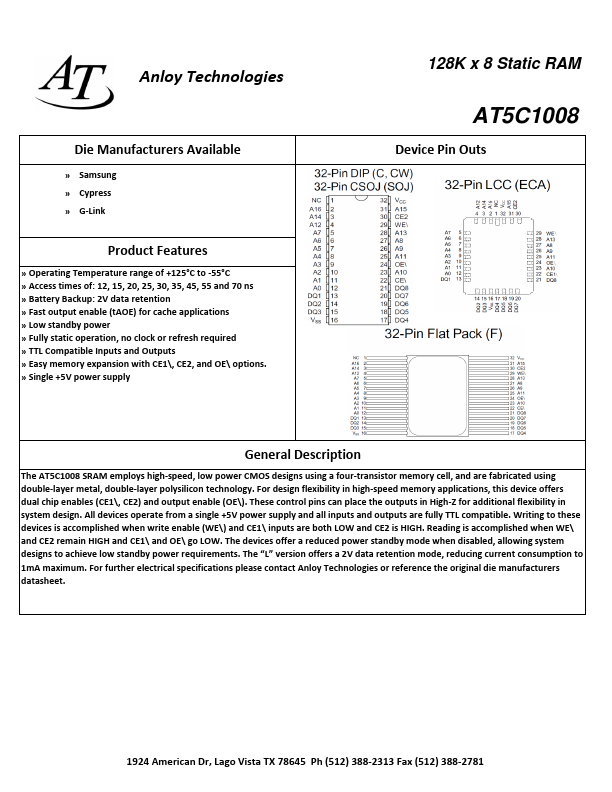

Device Pin Outs

General Description

The AT5C1008 SRAM employs high-speed, low power CMOS designs using a four-transistor memory cell, and are fabricated using double-layer metal, double-layer polysilicon technology. For design flexibility in high-speed memory applications, this device offers dual chip enables (CE1, CE2) and output enable (OE). These control pins can place the outputs in High-Z for additional flexibility in system design. All devices operate from a...