AP0100CS Overview

Key Specifications

Package: BGA

Mount Type: Surface Mount

Pins: 100

Max Operating Temp: 70 °C

Description

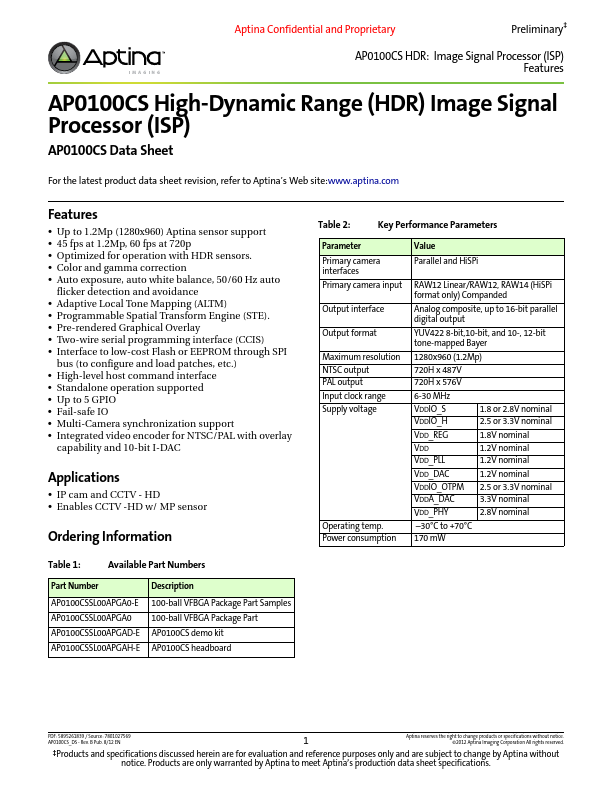

100-ball VFBGA Package Part Samples 100-ball VFBGA Package Part AP0100CS demo kit AP0100CS headboard Table 2: Key Performance Parameters Parameter Primary camera interfaces Primary camera input Output interface Output format Maximum resolution NTSC output PAL output Input clock range Supply voltage Operating temp. Power consumption Value Parallel and HiSPi RAW12 Linear/RAW12, RAW14 (HiSPi format only) Companded Analog composite, up to 16-bit parallel digital output YUV422 8-bit,10-bit, and 10-, 12-bit tone-mapped Bayer 1280x960 (1.2Mp) 720H x 487V 720H x 576V 6-30 MHz VDDIO_S 1.8 or 2.8V nominal VDDIO_H 2.5 or 3.3V nominal VDD_REG 1.8V nominal VDD 1.2V nominal VDD_PLL 1.2V nominal VDD_DAC 1.2V nominal.

Key Features

- Up to 1.2Mp (1280x960) Aptina sensor support

- 45 fps at 1.2Mp, 60 fps at 720p

- Optimized for operation with HDR sensors

- Color and gamma correction

- Auto exposure, auto white balance, 50/60 Hz auto flicker detection and avoidance