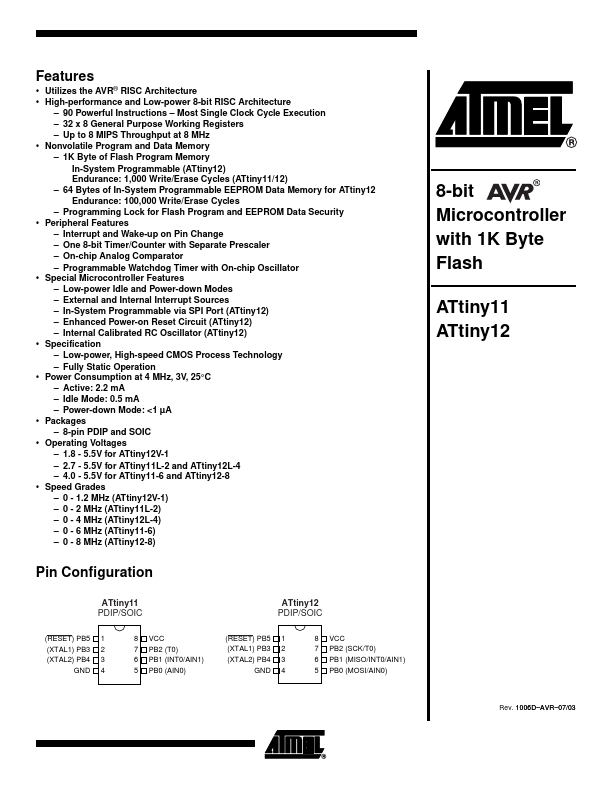

ATtiny12

Overview

- Utilizes the AVR® RISC Architecture

- High-performance and Low-power 8-bit RISC Architecture - 90 Powerful Instructions - Most Single Clock Cycle Execution - 32 x 8 General Purpose Working Registers - Up to 8 MIPS Throughput at 8 MHz

- Nonvolatile Program and Data Memory - 1K Byte of Flash Program Memory In-System Programmable (ATtiny12) Endurance: 1,000 Write/Erase Cycles (ATtiny11/12) - 64 Bytes of In-System Programmable EEPROM Data Memory for ATtiny12 Endurance: 100,000 Write/Erase Cycles - Programming Lock for Flash Program and EEPROM Data Security

- Peripheral Features - Interrupt and Wake-up on Pin Change - One 8-bit Timer/Counter with Separate Prescaler - On-chip Analog Comparator - Programmable Watchdog Timer with On-chip Oscillator

- Special Microcontroller Features - Low-power Idle and Power-down Modes - External and Internal Interrupt Sources - In-System Programmable via SPI Port (ATtiny12) - Enhanced Power-on Reset Circuit