AS4DDR232M64PBG

AS4DDR232M64PBG is 32Mx64 DDR2 SDRAM iNTEGRATED Plastic Encapsulated Microcircuit manufactured by Austin Semiconductor.

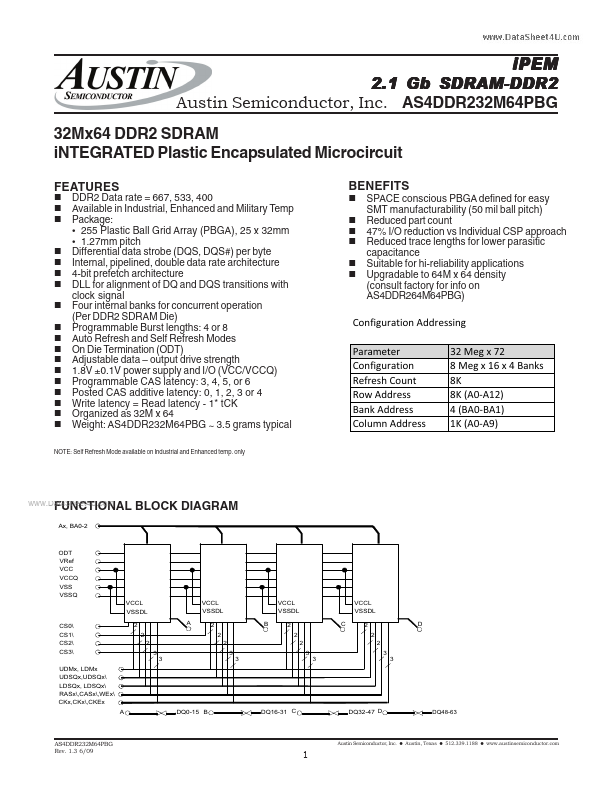

i PEM 2.1 G b SDRAM-DDR2 Gb Austin Semiconductor, Inc. AS4DDR232M64PBG 32Mx64 DDR2 SDRAM i NTEGRATED Plastic Encapsulated Microcircuit

Features

- -

- -

- -

- -

- -

- -

- -

- -

- - DDR2 Data rate = 667, 533, 400 Available in Industrial, Enhanced and Military Temp Package:

- 255 Plastic Ball Grid Array (PBGA), 25 x 32mm

- 1.27mm pitch Differential data strobe (DQS, DQS#) per byte Internal, pipelined, double data rate architecture 4-bit prefetch architecture DLL for alignment of DQ and DQS transitions with clock signal Four internal banks for concurrent operation (Per DDR2 SDRAM Die) Programmable Burst lengths: 4 or 8 Auto Refresh and Self Refresh Modes On Die Termination (ODT) Adjustable data

- output drive strength 1.8V ±0.1V power supply and I/O (VCC/VCCQ) Programmable CAS latency: 3, 4, 5, or 6 Posted CAS additive latency: 0, 1, 2, 3 or 4 Write latency = Read latency

- 1- t CK Organized as 32M x 64 Weight: AS4DDR232M64PBG ~ 3.5 grams typical

BENEFITS

- -

- -

- - SPACE conscious PBGA defined for easy SMT manufacturability (50 mil ball pitch) Reduced part count 47% I/O reduction vs Individual CSP approach Reduced trace lengths for lower parasitic capacitance Suitable for hi-reliability applications Upgradable to 64M x 64 density (consult factory for info on AS4DDR264M64PBG)

Configuration Addressing Parameter Configuration Refresh Count Row Address Bank Address Column Address 32Megx72 8Megx16x4Banks 8K 8K(A0ͲA12) 4(BA0ͲBA1) 1K(A0ͲA9)

NOTE: Self Refresh Mode available on Industrial and Enhanced temp. only

.. FUNCTIONAL

Ax, BA0-2

BLOCK DIAGRAM

ODT VRef VCC VCCQ VSS VSSQ VCCL VSSDL CS0 CS1 CS2 CS3 UDMx, LDMx UDSQx,UDSQx LDSQx, LDSQx RASx,CASx,WEx CKx,CKx,CKEx A DQ0-15 B DQ16-31 C DQ32-47 D

DQ48-63

VCCL VSSDL A 2 2 2 3 3 3 3 B

VCCL VSSDL 2 2 2 3 3 C

VCCL VSSDL 2 2 2 3 3 D

2 2...