AS4LC4M16

AS4LC4M16 is 4 MEG x 16 DRAM manufactured by Austin Semiconductor.

FEATURES

- Single +3.3V ±0.3V power supply.

- Industry-standard x16 pinout, timing, functions, and package.

- 12 row, 10 column addresses

- High-performance CMOS silicon-gate process

- All inputs, outputs and clocks are LVTTL-patible

- Extended Data-Out (EDO) PAGE MODE access

- 4,096-cycle CAS-BEFORE-RAS (CBR) REFRESH distributed across 64ms

- Optional self refresh (S) for low-power data retention

- Level 1 Moisture Sensitivity Rating, JEDEC J-STD-020

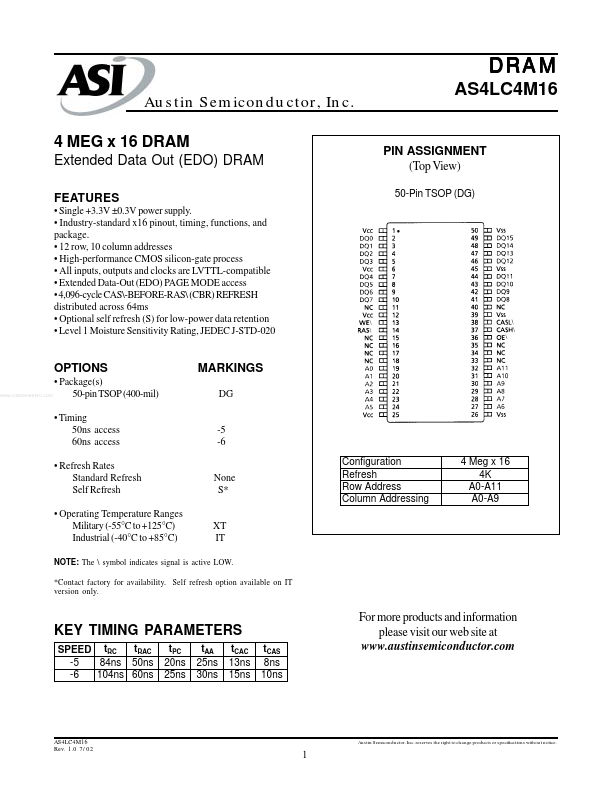

PIN ASSIGNMENT (Top View)

50-Pin TSOP (DG)

OPTIONS

- Package(s) 50-pin TSOP (400-mil) ..

- Timing 50ns access 60ns access

- Refresh Rates Standard Refresh Self Refresh

- Operating Temperature Ranges Military (-55°C to +125°C) Industrial (-40°C to +85°C)

MARKINGS

-5 -6

Configuration Refresh Row Address Column Addressing 4 Meg x 16 4K A0-A11 A0-A9

None S-

XT IT

NOTE: The symbol indicates signal is active LOW.

- Contact factory for availability. Self refresh option available on IT version only.

KEY TIMING PARAMETERS t RAC SPEED t RC -5 84ns 50ns -6 104ns 60ns t PC 20ns 25ns t AA 25ns 30ns t CAC 13ns 15ns t CAS 8ns 10ns

For more products and information please visit our web site at .austinsemiconductor.

AS4LC4M16 Rev. 1.0 7/02

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

DRAM

Austin Semiconductor, Inc. FUNCTIONAL BLOCK DIAGRAM

AS4LC4M16 Rev. 1.0 7/02

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

DRAM

Austin Semiconductor, Inc.

GENERAL DESCRIPTION

The 4 Meg x 16 DRAM is a high-speed CMOS, dynamic random-access memory device containing 67,108,864 bits and designed to operate from 3V to 3.6V. The device is functionally organized as 4,194,304 locations containing 16 bits each. The 4,194,304 memory locations are arranged in 4,096 rows by 1,024 columns. During READ or WRITE cycles, each location is uniquely addresses via the address bits: 12 row-address bits (A0

- A11) and 10...