AS4SD16M16

AS4SD16M16 is 16 Meg x 16 SDRAM Synchronous DRAM Memory manufactured by Austin Semiconductor.

FEATURES

- Full Military temp (-55°C to 125°C) processing available

- Configuration: 16 Meg x 16 (4 Meg x 16 x 4 banks)

- Fully synchronous; all signals registered on positive edge of system clock

- Internal pipelined operation; column address can be changed every clock cycle

- Internal banks for hiding row access/precharge

- Programmable burst lengths: 1, 2, 4, 8 or full page

- Auto Precharge, includes CONCURRENT AUTO PRECHARGE and Auto Refresh Modes

- Self Refresh Mode (IT)

- 64ms, 8,192-cycle refresh (IT)

- <24ms 8,192 cycle recfresh (XT)

- WRITE Recovery (t WR = “2 CLK”)

- LVTTL-patible inputs and outputs ..

- Single +3.3V ±0.3V power supply

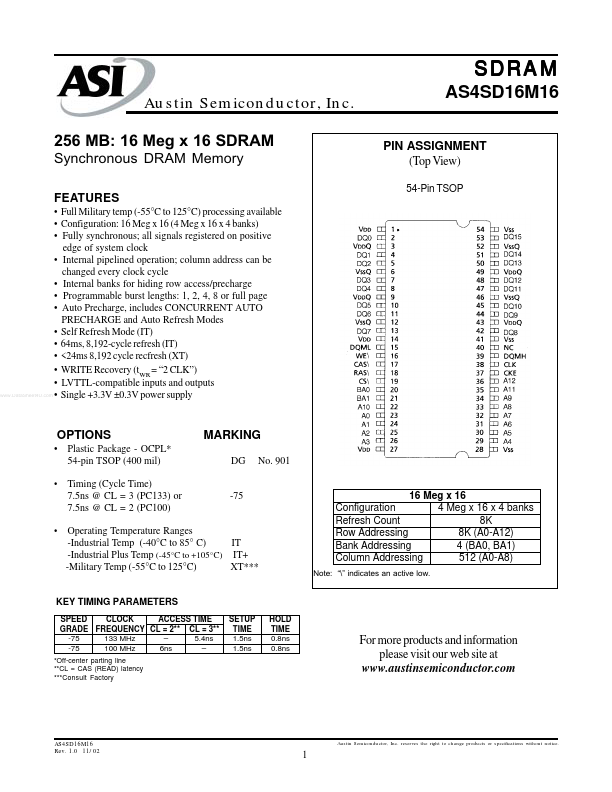

PIN ASSIGNMENT (Top View)

54-Pin TSOP

OPTIONS

- Plastic Package

- OCPL- 54-pin TSOP (400 mil) Timing (Cycle Time) 7.5ns @ CL = 3 (PC133) or 7.5ns @ CL = 2 (PC100)

MARKING

DG No. 901

- -75

- Operating Temperature Ranges -Industrial Temp (-40°C to 85° C) IT -Industrial Plus Temp (-45°C to +105°C) IT+ -Military Temp (-55°C to 125°C) XT-

- -

16 Meg x 16 Configuration 4 Meg x 16 x 4 banks Refresh Count 8K Row Addressing 8K (A0-A12) Bank Addressing 4 (BA0, BA1) Column Addressing 512 (A0-A8)

Note: “” indicates an active low.

KEY TIMING PARAMETERS

SPEED CLOCK ACCESS TIME GRADE FREQUENCY CL = 2-

- CL = 3-

- -75 133 MHz

- 5.4ns -75 100 MHz 6ns

- - Off-center parting line

- - CL = CAS (READ) latency

- -

- Consult Factory

SETUP TIME 1.5ns 1.5ns

HOLD TIME 0.8ns 0.8ns

For more products and information please visit our web site at .austinsemiconductor.

AS4SD16M16 Rev. 1.0 11/02

Austin Semiconductor, Inc. reserves the right to change products or specifications without...