AS5SP512K18DQ

AS5SP512K18DQ is Plastic Encapsulated Microcircuit 9Mb manufactured by Austin Semiconductor.

COTS PEM

Austin Semiconductor, Inc. AS5SP512K18DQ SSRAM

9Mb, 512K x 18, Synchronous SRAM

Pipeline Burst, Single Cycle Deselect

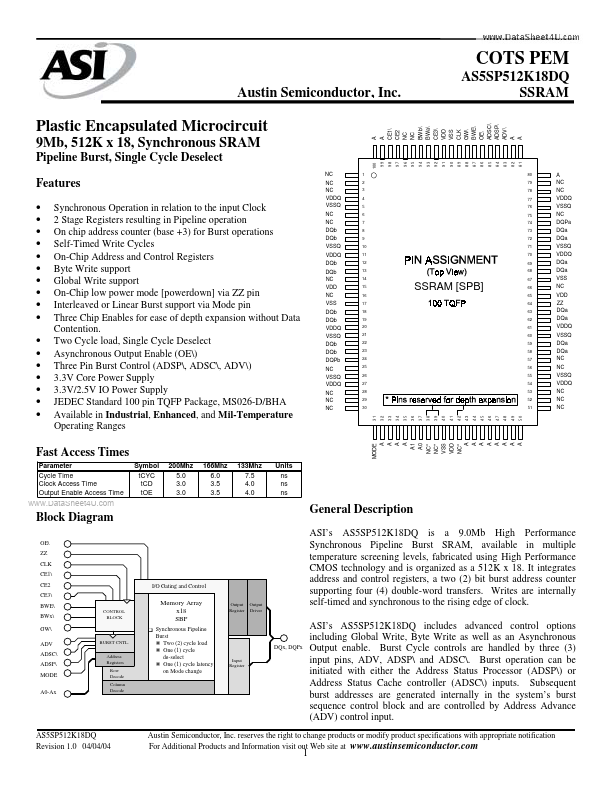

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30

A A CE1 CE2 NC NC BWb BWa CE3 VDD VSS CLK GW BWE OE ADSC ADSP ADV A A

Plastic Encapsulated Microcircuit

80 79 78 77 76 75 74 73 72 71 70 69 68 67

Features

- -

- -

- -

- -

- -

- -

- -

- -

- Synchronous Operation in relation to the input Clock 2 Stage Registers resulting in Pipeline operation On chip address counter (base +3) for Burst operations Self-Timed Write Cycles On-Chip Address and Control Registers Byte Write support Global Write support On-Chip low power mode [powerdown] via ZZ pin Interleaved or Linear Burst support via Mode pin Three Chip Enables for ease of depth expansion without Data Contention. Two Cycle load, Single Cycle Deselect Asynchronous Output Enable (OE) Three Pin Burst Control (ADSP, ADSC, ADV) 3.3V Core Power Supply 3.3V/2.5V IO Power Supply JEDEC Standard 100 pin TQFP Package, MS026-D/BHA Available in Industrial, Enhanced, and Mil-Temperature Operating Ranges

NC NC VDDQ VSSQ NC NC DQb DQb VSSQ VDDQ DQb DQb NC VDD NC VSS DQb DQb VDDQ VSSQ DQb DQb DQPb NC VSSQ VDDQ NC NC NC

A NC NC VDDQ VSSQ NC DQPa DQa DQa VSSQ VDDQ DQa DQa VSS NC VDD ZZ DQa DQa VDDQ VSSQ DQa DQa NC NC VSSQ VDDQ NC NC NC

SSRAM [SPB]

66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51

MODE A A A A A1 A0

Fast Access Times

Parameter Cycle Time Clock Access Time Output Enable Access Time Symbol t CYC t CD t OE 200Mhz 5.0 3.0 3.0 166Mhz 6.0 3.5 3.5 133Mhz 7.5 4.0 4.0 Units ns ns ns

..

Block Diagram

OE ZZ CLK CE1 CE2 CE3 BWE BWx GW ADV ADSC ADSP MODE A0-Ax

BURST CNTL. Address Registers Row Decode Column Decode CONTROL BLOCK

General...