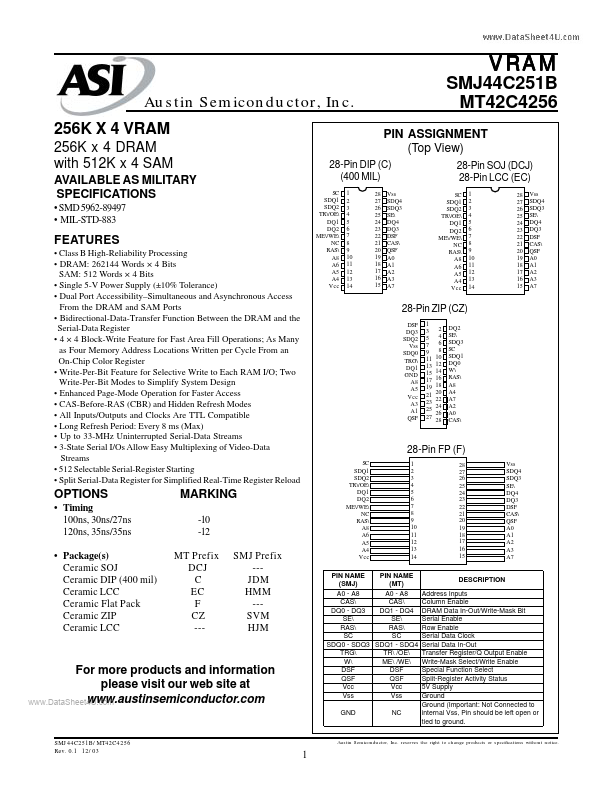

MT42C4256 Overview

Key Specifications

Operating Voltage: 5 V

Max Voltage (typical range): 5.5 V

Min Voltage (typical range): 4.5 V

Length: 36 mm

Key Features

- Class B High-Reliability Processing

- DRAM: 262144 Words × 4 Bits SAM: 512 Words × 4 Bits

- Single 5-V Power Supply (±10% Tolerance)

- Dual Port Accessibility–Simultaneous and Asynchronous Access From the DRAM and SAM Ports

- Bidirectional-Data-Transfer Function Between the DRAM and the Serial-Data Register