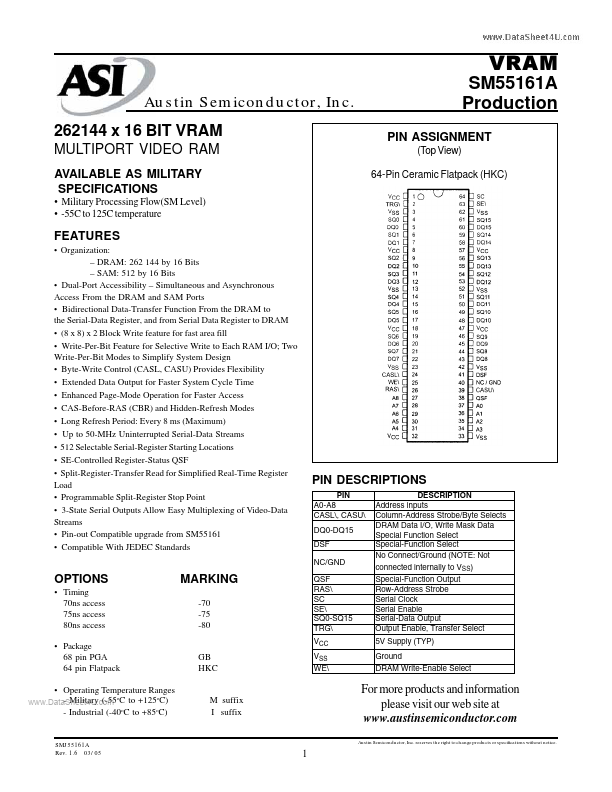

SM55161A Overview

Key Features

- Organization: – DRAM: 262 144 by 16 Bits – SAM: 512 by 16 Bits

- Dual-Port Accessibility – Simultaneous and Asynchronous Access From the DRAM and SAM Ports

- Bidirectional Data-Transfer Function From the DRAM to the Serial-Data Register, and from Serial Data Register to DRAM

- x 2 Block Write feature for fast area fill

- Write-Per-Bit Feature for Selective Write to Each RAM I/O; Two Write-Per-Bit Modes to Simplify System Design