HCPL-0710

HCPL-0710 is 40 ns Propagation Delay / CMOS Optocoupler manufactured by Avago Technologies.

- Part of the HCPL-7710 comparator family.

- Part of the HCPL-7710 comparator family.

Description

Features

Available in either an 8-pin DIP or SO-8 package style respectively, the HCPL-7710 or HCPL-0710 optocouplers utilize the latest CMOS IC technology to achieve outstanding performance with very low power consumption. The HCPL-x710 require only two bypass capacitors for plete CMOS patibility.

- +5 V CMOS patibility

- 8 ns maximum pulse width distortion

- 20 ns maximum prop. delay skew

- High speed: 12 Mbd

- 40 ns maximum prop. delay

Basic building blocks of the HCPL-x710 are a CMOS LED driver IC, a high speed LED and a CMOS detector IC. A

- 10 k V/µs minimum mon mode rejection

- -40°C to 100°C temperature range

CMOS logic input signal controls the LED driver IC, which supplies current to the LED. The detector IC incorporates an integrated photodiode, a high-speed transimpedance amplifier, and a voltage parator with an output driver.

- Safety and regulatory approvals UL Recognized 3750 Vrms for 1 min. per UL 1577 5000 Vrms for 1 min. per UL 1577 (for HCPL-7710 option 020)

CSA ponent Acceptance Notice #5

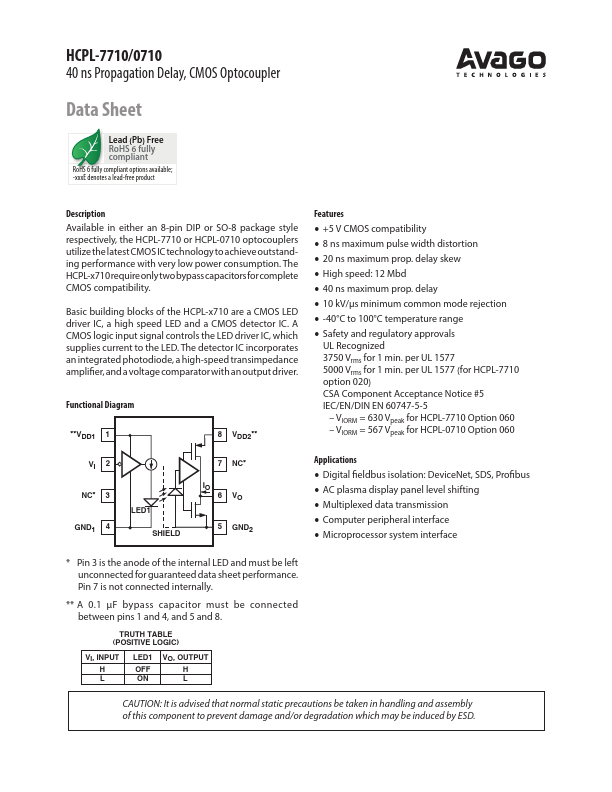

Functional Diagram

IEC/EN/DIN EN 60747-5-5

- - VDD1 1

8 VDD2-

- TRUT- HVTIOARBML=E630 Vpeak for HCPL-7710 Option 060 (POSIT- IVVEIOLROMG=IC5)67 Vpeak for HCPL-0710 Option 060

VI, INPUT LED1 VO, OUTPUT

VI 2

7 NC-

Appl Oi Oc Fa Nt Fions

- Digital fieldbus isolation: Device Net, SDS, Profibus

NC- 3 GND1 4

LED1 SHIELD

IO 6 VO 5 GND2

- AC plasma display panel level shifting

- Multiplexed data transmission

- puter peripheral interface

- Microprocessor system interface

- Pin 3 is the anode of the internal LED and must be left unconnected for guaranteed data sheet performance. Pin 7 is not connected internally.

- - A 0.1 µF bypass capacitor must be connected between pins 1 and 4, and 5 and 8.

8 VDD2-

- 7 NC-

TRUTH TABLE (POSITIVE LOGIC)

VI,...