AUR3852

AUR3852 is Enhanced Multi-touch Capacitive Touch Screen Controller manufactured by BCD.

Data Sheet

Enhanced Multi-touch Capacitive Touch Screen Controller AUR3852

General Description

The AUR3852 is a low-cost high-resolution single chip solution for APA capacitive touch screen. It is an 8-bit single cycle 8051 microcontroller with ICP Interface. The chip includes a 12-bit successive approximation analog-to-digital converter with an I2C interface and multiplexer-switcher circuits for flexible measurement of analog signal from APA panel. An accurate switched-capacitor integrator is built-in and it can auto calibrate the pixel parameters for a wide range of capacitance on the touch screen (0.1p F to 4p F). On-chip capacitor can replace external ponent. This touch screen controller (TSC) with CMOS integration circuit provides an ideal choice for APA touch panel. The AUR3852 is specified over the temperature range of -40°C to 85°C.

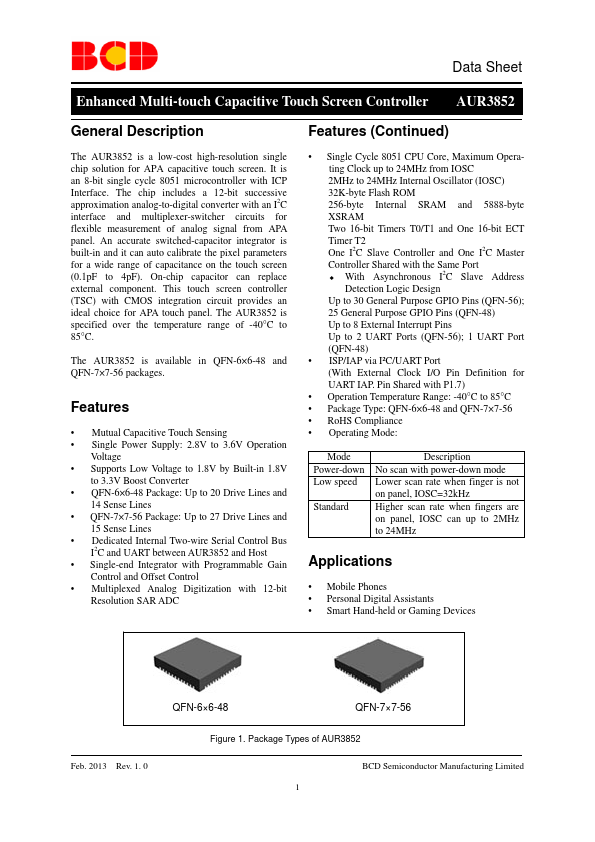

The AUR3852 is available in QFN-6×6-48 and QFN-7×7-56 packages.

Features

- 1Mutual Capacitive Touch Sensing

- Single Power Supply: 2.8V to 3.6V Operation

Voltage

- 1Supports Low Voltage to 1.8V by Built-in 1.8V to 3.3V Boost Converter

- QFN-6×6-48 Package: Up to 20 Drive Lines and

14 Sense Lines

- 1QFN-7×7-56 Package: Up to 27 Drive Lines and

15 Sense Lines

- 1Dedicated Internal Two-wire Serial Control Bus

I2C and UART between AUR3852 and Host

- 1Single-end Integrator with Programmable Gain

Control and Offset Control

- 1Multiplexed Analog Digitization with 12-bit

Resolution SAR ADC

Features

(Continued)

- Single Cycle 8051 CPU Core, Maximum Operating Clock up to 24MHz from IOSC 2MHz to 24MHz Internal Oscillator (IOSC) 32K-byte Flash ROM 256-byte Internal SRAM and 5888-byte XSRAM Two 16-bit Timers T0/T1 and One 16-bit ECT Timer T2 One I2C Slave Controller and One I2C Master Controller Shared with the Same Port With Asynchronous I2C Slave Address Detection Logic Design Up to 30 General Purpose GPIO Pins (QFN-56); 25 General Purpose GPIO Pins (QFN-48) Up to 8 External Interrupt Pins Up to 2 UART Ports (QFN-56); 1 UART Port...