AFE1230

AFE1230 is G.SHDSL ANALOG FRONT-END manufactured by Burr-Brown.

- Part of the AFE1230-Burr comparator family.

- Part of the AFE1230-Burr comparator family.

SBWS015A

- AUGUST 2001

G.SHDSL ANALOG FRONT-END

Features q E1, T1, AND SUBRATE OPERATION q PLIES WITH G.SHDSL AND HDSL2 q 16-BIT, DELTA-SIGMA CONVERTERS q ON-CHIP DRIVER AND PGA q PROGRAMMABLE tx AND rx FILTERS q SERIAL DIGITAL INTERFACE q 750mW POWER DISSIPATION AT E1 q +5V POWER (5V OR 3.3V DIGITAL) q SSOP-28 PACKAGE q

- 40°C TO +85°C TEMPERATURE RANGE

DESCRIPTION

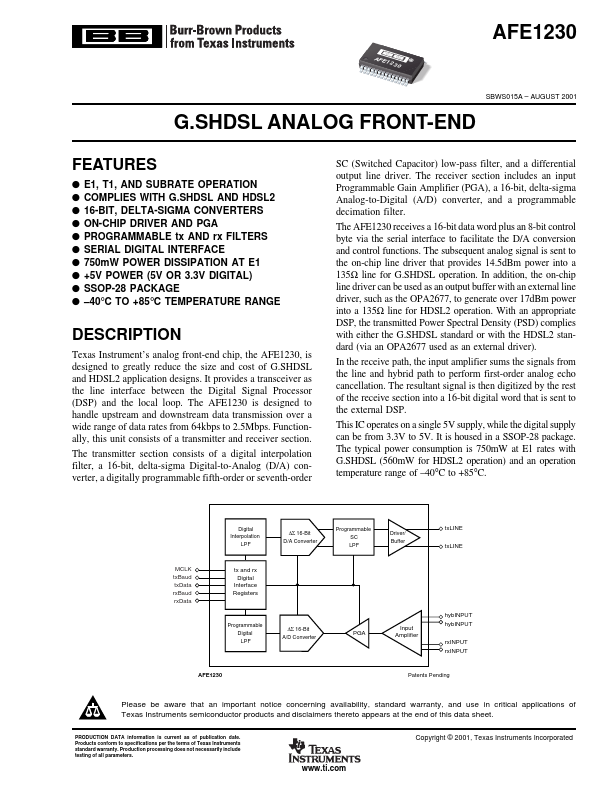

Texas Instrument’s analog front-end chip, the AFE1230, is designed to greatly reduce the size and cost of G.SHDSL and HDSL2 application designs. It provides a transceiver as the line interface between the Digital Signal Processor (DSP) and the local loop. The AFE1230 is designed to handle upstream and...