C8051 Datasheet Text

C8051 Legacy-Speed 8-Bit

Processor Core

General Description

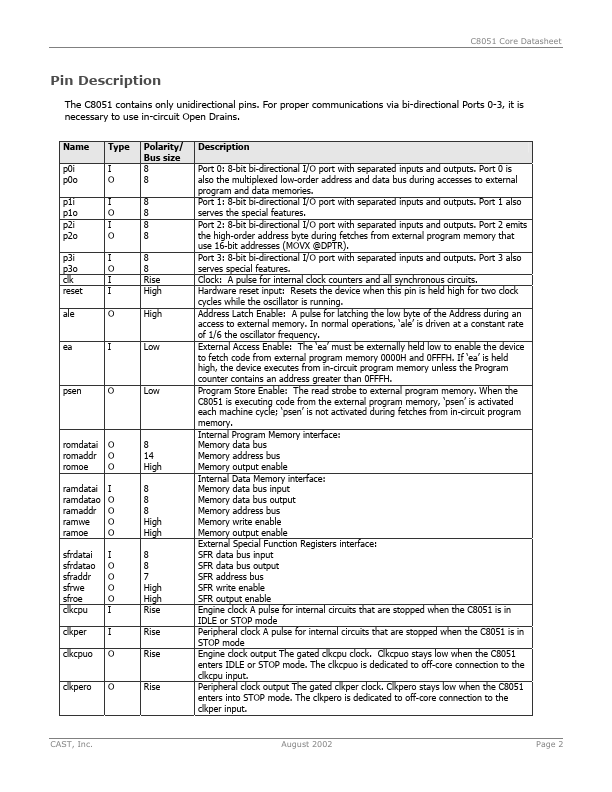

The C8051 processor core is a single-chip, 8-bit microcontroller that executes all ASM51 instructions and has the same instruction set and timing of the 80C31. On-chip debugging is an option.

The microcode-free design was developed for reuse in ASICs and FPGAs. It is strictly synchronous, with positive-edge clocking (except for a flip-flop for internal reset and two flip-flops for gated clocks in the PMU), no internal tri-states and a synchronous reset. Scan insertion is therefore straightforward.

Symbol reset C8051 clk p0i p1i ea p2i p3i ale psen p0o p1o clkcpu clkper p2o p3o clkcpuo clkpero ramdatai ramdatao sfrdatai sfrdatao sfraddr ramaddr ramwe ramoe sfroe sfrwe romdatai romaddr romoe

Features

- 8-bit Control Unit

- 8-bit Arithmetic-Logic Unit with 8-bit multiplication and division

- Instruction decoder

- Four 8-bit Input / Output ports

- Two 16-bit Timer/Counters

- Serial Peripheral Interface in full duplex mode

- Synchronous mode, fixed baud rate

- 8-bit & 9-bit UART mode, variable baud rate

- 9-bit UART mode, fixed baud rate

- Multiprocessor munication

- Two Level Priority Interrupt System

- 5 Interrupt Sources

- Internal Clock prescaler and Phase Generator

- 256 bytes of Read/Write Data Memory Space

- 64KB External Program Memory Space

- 64KB External Data Memory Space

- Services up to 107 External Special Function

Registers

- Power Management Unit supports stop and idle modes

CAST, Inc.

August 2002

Page 1

C8051 Core Datasheet...