CP1181

CP1181 is 21 ch E1/T1 Mapper manufactured by CHIP.

Product Brief OPTRANS Series

CP1181_PB_Rev1.0 March, 2005

21 Channel E1/T1 Mapper

..

OVERVIEW

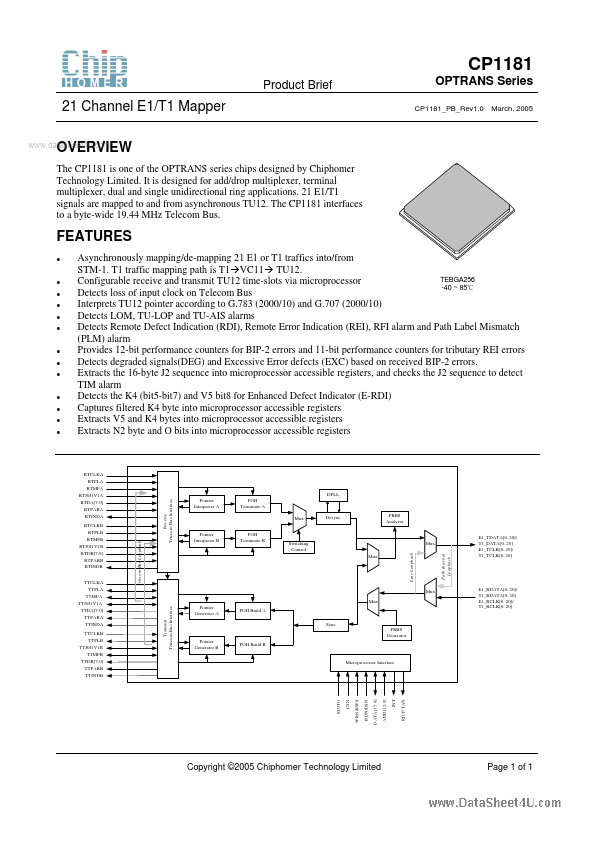

The CP1181 is one of the OPTRANS series chips designed by Chiphomer Technology Limited. It is designed for add/drop multiplexer, terminal multiplexer, dual and single unidirectional ring applications. 21 E1/T1 signals are mapped to and from asynchronous TU12. The CP1181 interfaces to a byte-wide 19.44 MHz Tele Bus.

Features

Asynchronously mapping/de-mapping 21 E1 or T1 traffics into/from STM-1. T1 traffic mapping path is T1 VC11 TU12. TEBGA256 Configurable receive and transmit TU12 time-slots via microprocessor -40 ~ 85℃ Detects loss of input clock on Tele Bus Interprets TU12 pointer according to G.783 (2000/10) and G.707 (2000/10) Detects LOM, TU-LOP and TU-AIS alarms Detects Remote Defect Indication (RDI), Remote Error Indication (REI), RFI alarm and Path Label Mismatch (PLM) alarm Provides 12-bit performance counters for BIP-2 errors and 11-bit performance counters for tributary REI errors Detects degraded signals(DEG) and Excessive Error defects (EXC) based on received BIP-2 errors. Extracts the 16-byte J2 sequence into microprocessor accessible registers, and checks the J2 sequence to detect TIM alarm Detects the K4 (bit5-bit7) and V5 bit8 for Enhanced Defect Indicator (E-RDI) Captures filtered K4 byte into microprocessor accessible registers Extracts V5 and K4 bytes into microprocessor accessible registers Extracts N2 byte and O bits into microprocessor accessible registers

Receive Tele Bus Interface

RTCLKA RTPLA RTMFA RTJ0J1V1A RTDA[7:0] RTPARA RTINDA RTCLKB RTPLB RTMFB RTJ0J1V1B RTDB[7:0] RTPARB RTINDB TTCLKA TTPLA TTMFA TTJ0J1V1A TTDA[7:0] TTPARA TTINDA TTCLKB TTPLB TTJ0J1V1B TTMFB TTDB[7:0] TTPARB TTINDB

DPLL Pointer Interpreter A POH Terminate A Mux Desync PRBS Analyzer

Tele Bus Loopback

Pointer Interpreter B

POH Terminate B

Switching Control

Line Loopback

Mux Mux

Path Internal Loopback

E1_TDATA[0..20]/...