Datasheet Summary

High Speed Super Low Power SRAM

512K Word By 8 Bit

Revision History

Rev. No. 2.0 2.1

History Initial issue with new naming rule Add a new 32L WSON

- 8x8mm package

Issue Date Jan.26, 2005 Aug.12, 2005

Rev. 2.1

Chiplus reserves the right to change product or specification without notice.

High Speed Super Low Power SRAM

512K Word By 8 Bit

GENERAL DESCRIPTION

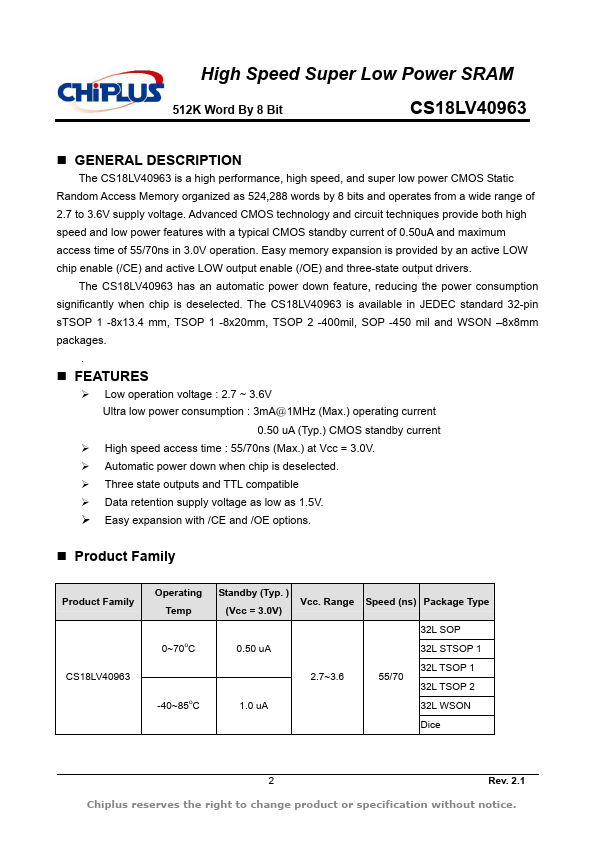

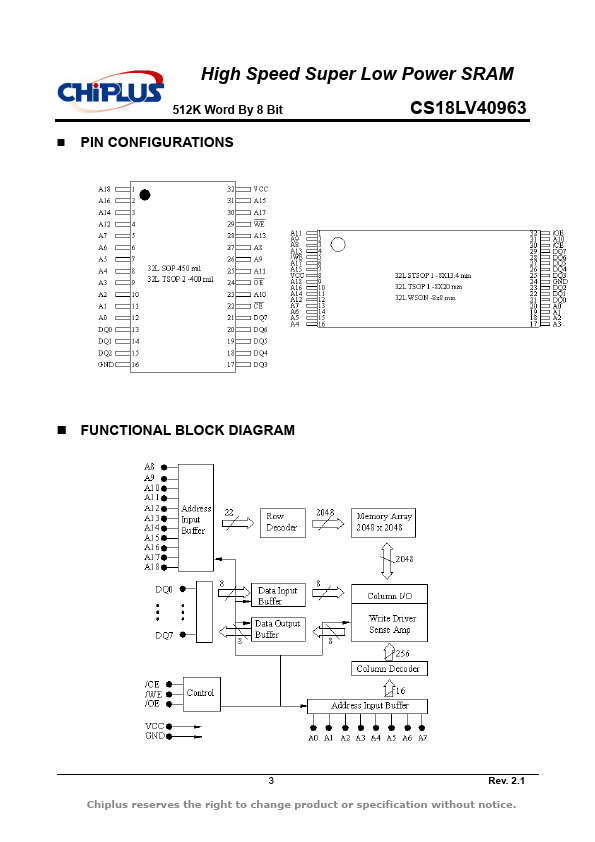

The CS18LV40963 is a high performance, high speed, and super low power CMOS Static Random Access Memory organized as 524,288 words by 8 bits and operates from a wide range of 2.7 to 3.6V supply voltage. Advanced CMOS technology and circuit techniques provide both high speed and low power Features with a...