CMX980A

Key Features

- RRC Filters for both Tx and Rx

- π/4 DQPSK Modulation

- 4 x 10-Bit D-A and 4 Input 10-Bit A-D

- Transmit Output Power Control

- 2 x 14-Bit Resolution Sigma Delta D-A

- Low Power 3.0 - 5.5Volt Operation

- 2 x 16-Bit Resolution Sigma Delta A-D

- Effective Power down Modes

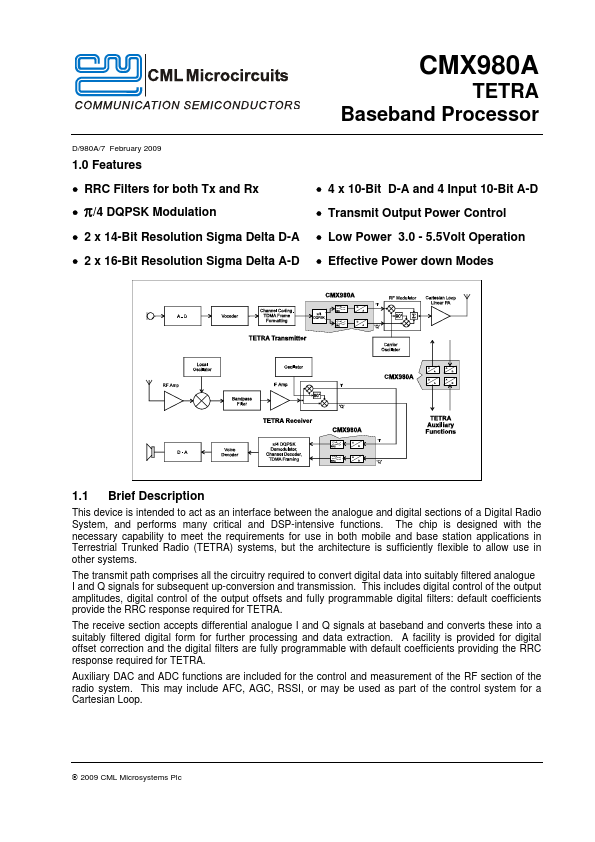

- 1 Brief Description This device is intended to act as an interface between the analogue and digital sections of a Digital Radio System, and performs many critical and DSP-intensive functions. The chip is designed with the necessary capability to meet the requirements for use in both mobile and base station applications in Terrestrial Trunked Radio (TETRA) systems, but the architecture is sufficiently flexible to allow use in other systems. The transmit path comprises all the circuitry required to convert digital data into suitably filtered analogue I and Q signals for subsequent up-conversion and transmission. This includes digital control of the output amplitudes, digital control of the output offsets and fully programmable digital filters: default coefficients provide the RRC response required for TETRA. The receive section accepts differential analogue I and Q signals at baseband and converts these into a suitably filtered digital form for further processing and data extraction. A facility is provided for digital offset correction and the digital filters are fully programmable with default coefficients providing the RRC response required for TETRA. Auxiliary DAC and ADC functions are included for the control and measurement of the RF section of the radio system. This may include AFC, AGC, RSSI, or may be used as part of the control system for a Cartesian Loop. © 2009 CML Microsystems Plc TETRA Baseband Processor CMX980A Section CONTENTS Page