CVPD-925

Ultra-Low Noise

LVPECL VCXO

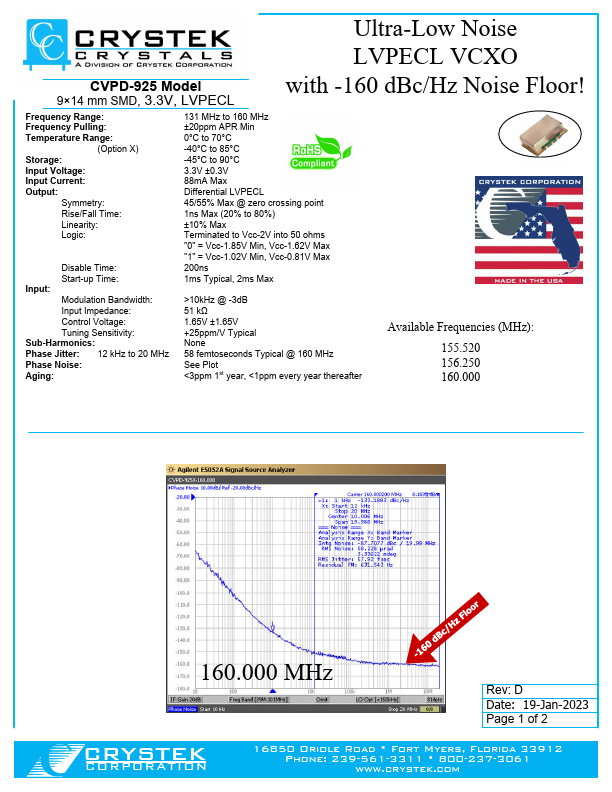

CVPD-925 Model 9×14 mm SMD, 3.3V, LVPECL with -160 d Bc/Hz Noise Floor!

Frequency Range: Frequency Pulling: Temperature Range:

(Option X) Storage: Input Voltage: Input Current: Output:

Symmetry: Rise/Fall Time: Linearity: Logic:

Disable Time: Start-up Time: Input: Modulation Bandwidth: Input Impedance: Control Voltage: Tuning Sensitivity: Sub-Harmonics: Phase Jitter: 12 k Hz to 20 MHz Phase Noise: Aging:

131 MHz to 160 MHz ±20ppm APR Min 0°C to 70°C -40°C to 85°C -45°C to 90°C 3.3V ±0.3V 88m A Max Differential LVPECL 45/55% Max @ zero crossing point 1ns Max (20% to 80%) ±10% Max Terminated to Vcc-2V into 50 ohms "0" = Vcc-1.85V Min, Vcc-1.62V Max "1" = Vcc-1.02V Min, Vcc-0.81V Max 200ns 1ms Typical, 2ms Max

>10k Hz @ -3d B 51 kΩ 1.65V ±1.65V +25ppm/V Typical None 58 femtoseconds Typical @ 160 MHz See Plot <3ppm 1st year, <1ppm every year thereafter

Available Frequencies (MHz):

155.520 156.250 160.000

160.000 MHz

Rev: D Date: 19-Jan-2023 Page 1 of 2

C...