CL12464FF

Description

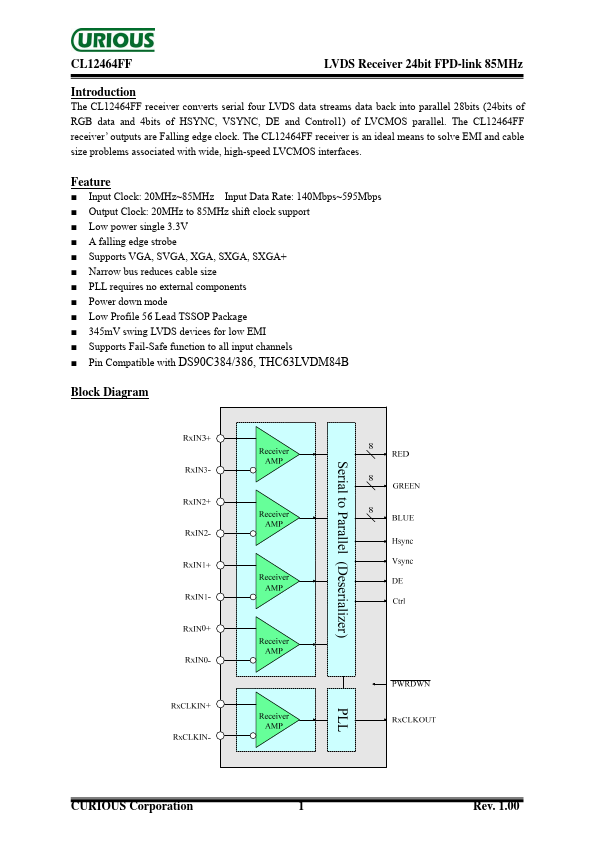

The CL12464FF receiver converts serial four LVDS data streams data back into parallel 28bits (24bits of RGB data and 4bits of HSYNC, VSYNC, DE and Control1) of LVCMOS parallel. The CL12464FF receiver’ outputs are Falling edge clock.

Key Features

- Input Clock: 20MHz~85MHz Input Data Rate: 140Mbps~595Mbps

- Output Clock: 20MHz to 85MHz shift clock support

- Low power single 3.3V

- A falling edge strobe

- Supports VGA, SVGA, XGA, SXGA, SXGA+

- Narrow bus reduces cable size

- PLL requires no external components

- Power down mode

- Low Profile 56 Lead TSSOP Package

- 345mV swing LVDS devices for low EMI