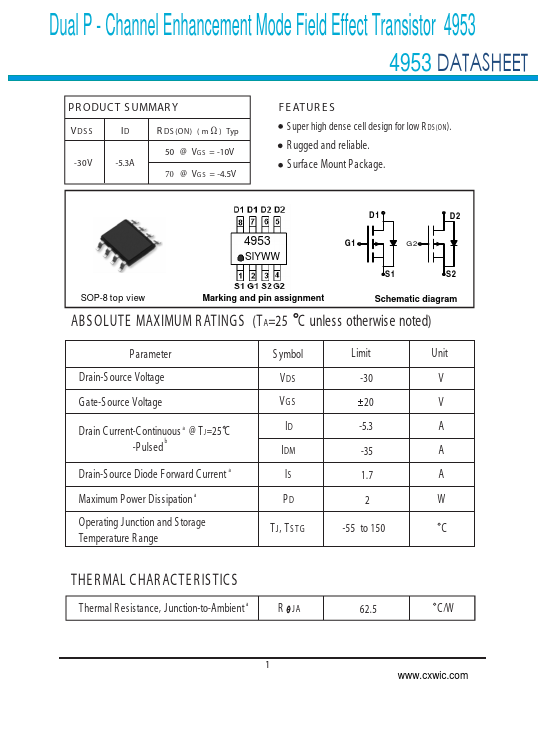

| Part | 4953 |

|---|---|

| Description | Dual P-Channel MOSFET |

| Category | MOSFET |

| Manufacturer | CXW |

| Size | 534.76 KB |

Pricing from 0.113 USD, available from Future Electronics and DigiKey.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Future Electronics | 913 | 200+ : 0.113 USD 400+ : 0.111 USD 1000+ : 0.109 USD 2000+ : 0.108 USD |

View Offer |

| DigiKey | 23863 | 1+ : 0.26 USD 10+ : 0.197 USD 25+ : 0.1764 USD 100+ : 0.1494 USD |

View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| 4953GM | Advanced Power Electronics Corp | AP4953GM |

| 4957AGM | Advanced Power Electronics Corp | AP4957AGM |

| TS431 | Taiwan Semiconductor | 2.495V Programmable Shunt Voltage Reference |

| XR-495 | Exar | Pulse-Width Modulating Regulator |

| 4957AGM | VBsemi | Dual P-Channel MOSFET |