CS5156

CS5156 is CPU 5-Bit Nonsynchronous Buck Controller manufactured by Cherry Semiconductor Corporation.

Description

The CS5156 is a 5-bit nonsynchronous N-Channel buck controller. It is designed to provide unprecedented transient response for today’s demanding high-density, high-speed logic. The regulator operates using a proprietary control method, which allows a 100ns response time to load transients. The CS5156 is designed to operate over a 4.25-16V range (VCC) using 12V to power the IC and 5V as the main supply for conversion. The CS5156 is specifically designed to power Pentium® II processors and other high performance core logic. It includes the following features

: on board, 5-bit DAC, short circuit protection, 1.0% output tolerance, VCC monitor, and programmable soft start capability. The CS5156 is backwards patible with the 4-bit CS5151, allowing the mother board designer the capability of using either the CS5151 or the CS5156 with no change in layout. The CS5156 is available in 16 pin surface mount and DIP packages.

Features s N-Channel Design s Excess of 1MHz Operation s 100ns Transient Response s 5-Bit DAC s Backward patible with 4-Bit CS5150/5151 and Adjustable CS5120/5121 s 30ns Gate Rise/Fall Times s 1% DAC Accuracy s 5V & 12V Operation s Remote Sense s Programmable Soft Start s Lossless Short Circuit Protection

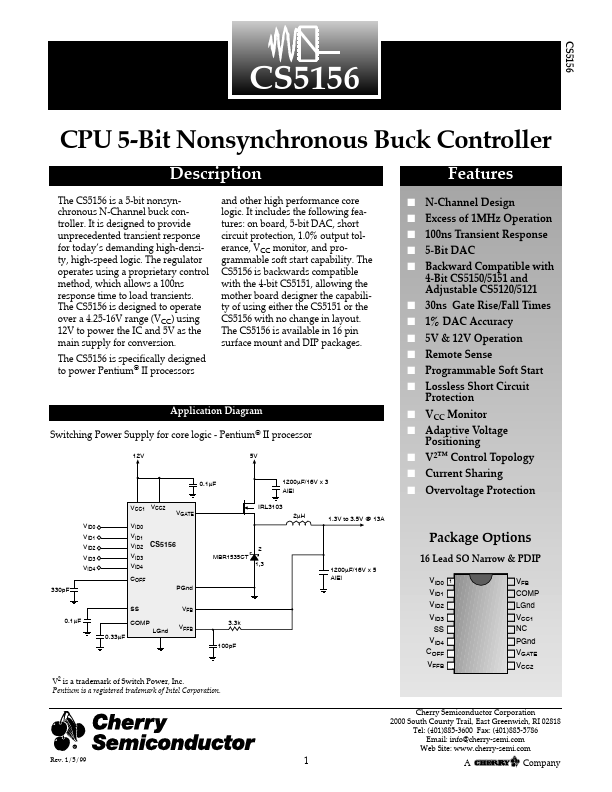

Application Diagram Switching Power Supply for core logic

- Pentium® II processor

12V 5V s VCC Monitor s Adaptive Voltage Positioning s V2™ Control Topology s Current Sharing s Overvoltage Protection

0.1µF VCC1 VCC2 VID0 VID1 VID2 VID3 VID4 330p F SS 0.1µF 0.33µF P LGnd VID0 VID1 VID2 VID3 VID4 COFF PGnd VFB VFFB 3.3k

1200µF/16V x 3 Al El IRL3103 2µ H 1.3V to 3.5V @ 13A

VGATE

MBR1535CT

Package Options

2 1,3

16 Lead SO Narrow & PDIP

1200µF/16V x 5 Al El

VID0 VID1 VID2 VID3 SS VID4 COFF VFFB

VFB P LGnd VCC1 NC PGnd VGATE VCC2

100p F

V2 is a trademark of Switch Power, Inc. Pentium is a registered trademark of Intel Corporation. Cherry Semiconductor Corporation 2000 South County Trail, East Greenwich, RI 02818 Tel: (401)885-3600...