CS5157H

CS5157H is CPU 5-Bit Synchronous Buck Controller manufactured by Cherry Semiconductor Corporation.

Description

The CS5157H is a 5-bit synchronous dual N-Channel buck controller. It is designed to provide unprecedented transient response for today’s demanding high-density, high-speed logic. The regulator operates using a proprietary control method, which allows a 100ns response time to load transients. The CS5157H is designed to operate over a 4.25-20V range (VCC) using 12V to power the IC and 5V or 12Vas the main supply for conversion. The CS5157H is specifically designed to power Pentium® II processors and other high performance core logic. It includes the following features

: on board, 5-bit DAC, short circuit protection, 1.0% output tolerance, VCC monitor, and programmable soft start capability. The CS5157H is available in 16 pin surface mount.

Features s Dual N-Channel Design s Excess of 1MHz Operation s 100ns Transient Response s 5-Bit DAC s Backward patible with Adjustable CS5120/5121 s 30ns Gate Rise/Fall Times s 1% DAC Accuracy s 5V & 12V Operation s Remote Sense s Programmable Soft Start s Lossless Short Circuit Protection

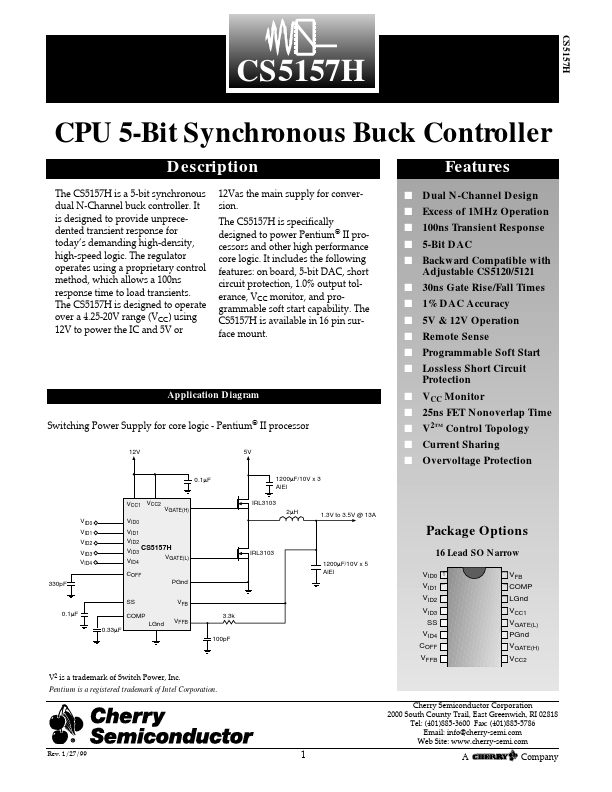

Application Diagram Switching Power Supply for core logic

- Pentium® II processor

12V 5V s VCC Monitor s 25ns FET Nonoverlap Time s V2TM Control Topology s Current Sharing s Overvoltage Protection

1200µF/10V x 3 Al El

0.1µF

VCC1 VCC2 VID0 VID1 VID2 VID3 VID4 330p F SS 0.1µF 0.33µF P LGnd VID0 VID1 VID2

VGATE(H)

IRL3103 2µ H 1.3V to 3.5V @ 13A

Package Options

IRL3103 1200µF/10V x 5 Al El

VID3 CS5157H VGATE(L) VID4 COFF PGnd VFB VFFB 3.3k

16 Lead SO Narrow

VID0 VID1 VID2 VID3 SS VID4 COFF VFFB

VFB P LGnd VCC1 VGATE(L) PGnd VGATE(H) VCC2

100p F

V2 is a trademark of Switch Power, Inc. Pentium is a registered trademark of Intel Corporation. Cherry Semiconductor Corporation 2000 South County Trail, East Greenwich, RI 02818 Tel: (401)885-3600 Fax: (401)885-5786 Email: info@cherry-semi. Web Site: .cherry-semi.

Rev. 1/27/99

® pany

Absolute Maximum Ratings Pin Name Max Operating Voltage Max Current VCC1

- . ....