CS5371

CS5371 is Low-power High-performance Modulators manufactured by Cirrus Logic.

Features

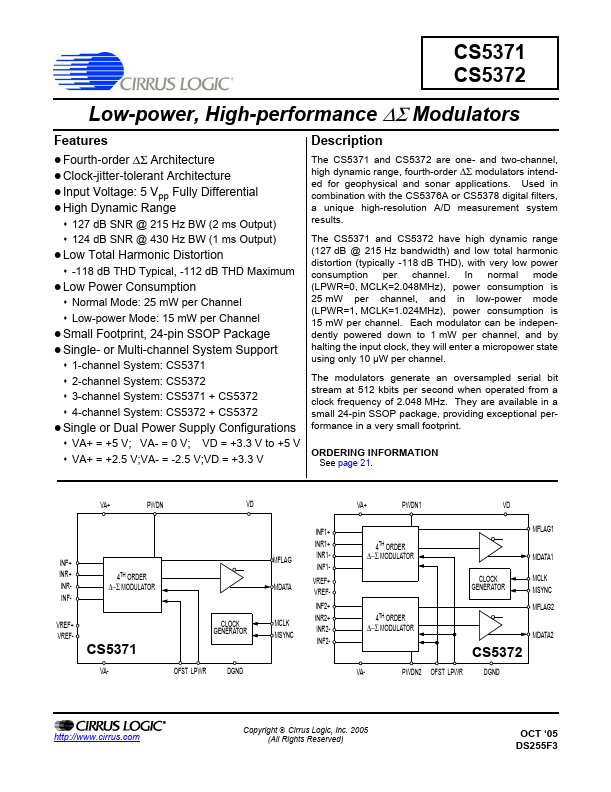

& Description z Fourth-order ∆Σ Architecture z Clock-jitter-tolerant Architecture z Input Voltage: 5 Vpp Fully Differential z High Dynamic Range

127 d B SNR @ 215 Hz BW (2 ms Output) 124 d B SNR @ 430 Hz BW (1 ms Output) z Low Total Harmonic Distortion

-118 d B THD Typical, -112 d B THD Maximum z Low Power Consumption

Normal Mode: 25 m W per Channel Low-power Mode: 15 m W per Channel z Small Footprint, 24-pin SSOP Package z Single- or Multi-channel System Support

1-channel System: CS5371 2-channel System: CS5372 3-channel System: CS5371 + CS5372 4-channel System: CS5372 + CS5372 z Single or Dual Power Supply Configurations

VA+ = +5 V; VA- = 0 V; VD = +3.3 V to +5 V VA+ = +2.5 V;VA- = -2.5 V;VD = +3.3 V

Description

The CS5371 and CS5372 are one- and two-channel, high dynamic range, fourth-order ∆Σ modulators intended for geophysical and sonar applications. Used in bination with...