CS5531 Overview

Key Specifications

Package: SSOP

Mount Type: Surface Mount

Pins: 20

Operating Voltage: 5 V

Description

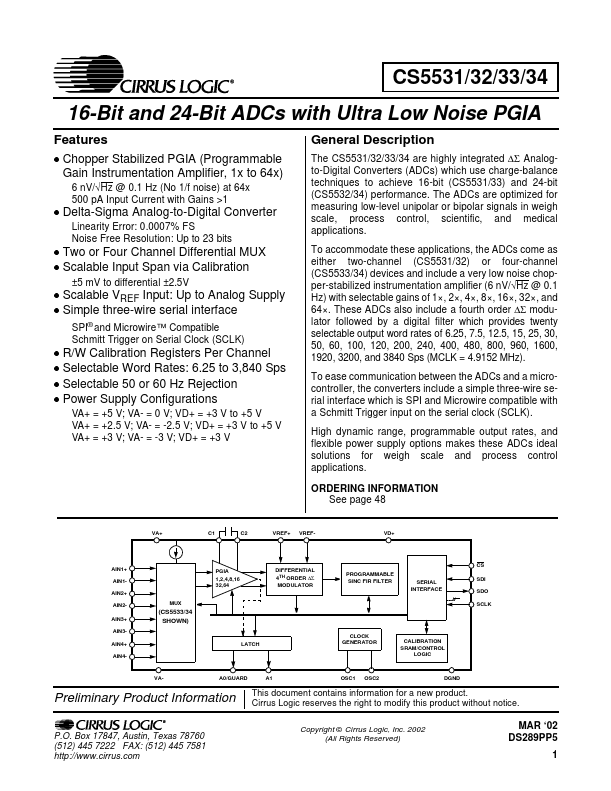

The CS5531/32/33/34 are highly integrated ∆Σ Analogto-Digital Converters (ADCs) which use charge-balance techniques to achieve 16-bit (CS5531/33) and 24-bit (CS5532/34) performance. The ADCs are optimized for measuring low-level unipolar or bipolar signals in weigh scale, process control, scientific, and medical applications.