1N4614UR-1

1N4614UR-1 is LEADLESS PACKAGE FOR SURFACE MOUNT manufactured by Compensated Deuices Incorporated.

- 1N4614UR-1 THRU 1N4627UR-1 AVAILABLE IN JAN, JANTX, JANTXV AND JANS

PER MIL-PRF-19500/435

1N4614UR-1 thru 1N4627UR-1 and CDLL4614 thru CDLL4627

- LEADLESS PACKAGE FOR SURFACE MOUNT

- LOW CURRENT OPERATION AT 250 µA

- METALLURGICALLY BONDED

MAXIMUM RATINGS

Operating Temperatures: -65°C to +175°C DC Power Dissipation: 500m W @ TEC = +125°C Power Derating: 10 m W / °C above TEC = +125°C Forward Voltage @ 200 m A: 1.1 Volts maximum

ELECTRICAL CHARACTERISTICS @ 25°C, unless otherwise specified.

CDI TYPE NUMBER NOMINAL ZENER VOLTAGE V @I Z ZT (Note 1) VOLTS CDLL4614 CDLL4615 CDLL4616 CDLL4617 CDLL4618 CDLL4619 CDLL4620 CDLL4621 CDLL4622 CDLL4623 CDLL4624 CDLL4625 CDLL4626 CDLL4627 1.8 2.0 2.2 2.4 2.7 3.0 3.3 3.6 3.9 4.3 4.7 5.1 5.6 6.2 ZENER TEST CURRENT I ZT MAXIMUM ZENER IMPEDANCE Z @I ZT ZT (Note 2) MAXIMUM REVERSE LEAKAGE CURRENT 1 @V R R MAXIMUM DC ZENER CURRENT

µ A

250 250 250 250 250 250 250 250 250 250 250 250 250 250

OHMS 1200 1250 1300 1400 1500 1600 1650 1700 1650 1600 1550 1500 1400 1200

µ A

7.5 5.0 4.0 2.0 1.0 0.8 7.5 7.5 5.0 4.0 10.0 10.0 10.0 10.0

VOLTS 1 1 1 1 1 1 1.5 2 2 2 3 3 4 5 m A 120 110 100 95 90 87 85 83 80 77 75 70 65 61

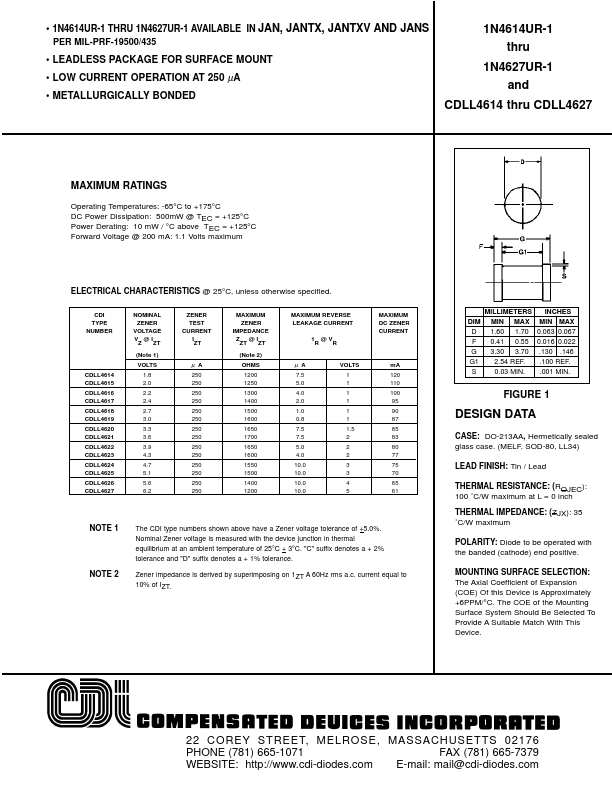

DIM D F G G1 S

MILLIMETERS INCHES MIN MAX MIN MAX 1.60 1.70 0.063 0.067 0.41 0.55 0.016 0.022 3.30 3.70 .130 .146 2.54 REF. .100 REF. 0.03 MIN. .001 MIN.

FIGURE 1

DESIGN DATA

CASE: DO-213AA, Hermetically sealed glass case. (MELF, SOD-80, LL34) LEAD FINISH: Tin / Lead THERMAL RESISTANCE: (ROJEC): 100 ˚C/W maximum at L = 0 inch THERMAL IMPEDANCE: (ZJX): 35 ˚C/W maximum POLARITY: Diode to be operated with the banded (cathode) end positive. MOUNTING SURFACE SELECTION: The Axial Coefficient of Expansion (COE) Of this Device is Approximately +6PPM/°C. The COE of the Mounting Surface System Should Be Selected To Provide A Suitable Match With This Device.

NOTE 1

The CDI type numbers shown above have a Zener voltage tolerance of +5.0%. Nominal Zener voltage is measured with the device junction in thermal equilibrium at an...