CY14B512P

Overview

- 512-Kbit nonvolatile static random access memory (nvSRAM) ❐ Internally organized as 64 K × 8 ❐ STORE to QuantumTrap nonvolatile elements initiated automatically on power-down (AutoStore) or by the user using HSB pin (Hardware STORE) or SPI instruction (Software STORE) ❐ RECALL to SRAM initiated on power-up (Power-Up RECALL) or by serial peripheral interface (SPI) instruction (Software RECALL) ❐ Automatic STORE on power-down with a small capacitor High reliability ❐ ❐ ❐ Write protection ❐ Hardware protection using Write Protect (WP) pin ❐ Software protection using Write Disable instruction ❐ Software block protection for 1/4, 1/2, or entire array Low power consumption ❐ Single 3 V + 20%, -10% operation ❐ Average active current of 10 mA at 40 MHz operation Industry standard configurations ❐ Industrial temperature ❐ 16-pin small outline integrated circuit (SOIC) package ❐ Restriction of hazardous substances (RoHS) compliant * *

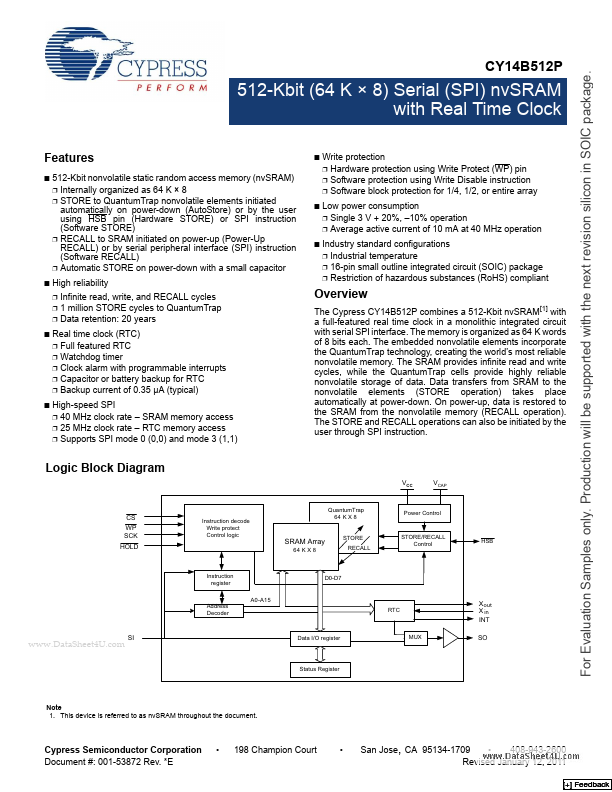

- Infinite read, write, and RECALL cycles 1 million STORE cycles to QuantumTrap Data retention: 20 years Overview The Cypress CY14B512P combines a 512-Kbit nvSRAM[1] with a full-featured real time clock in a monolithic integrated circuit with serial SPI interface. The memory is organized as 64 K words of 8 bits each. The embedded nonvolatile elements incorporate the QuantumTrap technology, creating the world’s most reliable nonvolatile memory. The SRAM provides infinite read and write cycles, while the QuantumTrap cells provide highly reliable nonvolatile storage of data. Data transfers from SRAM to the nonvolatile elements (STORE operation) takes place automatically at power-down. On power-up, data is restored to the SRAM from the nonvolatile memory (RECALL operation). The STORE and RECALL operations can also be initiated by the user through SPI instruction