CY14E512J

Key Features

- 512-Kbit nonvolatile static random access memory (nvSRAM) ❐ Internally organized as 64 K × 8 ❐ STORE to QuantumTrap nonvolatile elements initiated automatically on power-down (AutoStore) or by using I2C command (Software STORE) or HSB pin (Hardware STORE) ❐ RECALL to SRAM initiated on power-up (Power-Up RECALL) or by I2C command (Software RECALL) ❐ Automatic STORE on power-down with a small capacitor (except for CY14X512J1)

- High reliability Infinite read, write, and RECALL cycles 1 million STORE cycles to QuantumTrap ❐ Data retention: 20 years at 85 °C 2

- High speed I C interface ❐ Industry standard 100 kHz and 400 kHz speed ❐ Fast-mode Plus: 1 MHz speed ❐ High speed: 3.4 MHz ❐ Zero cycle delay reads and writes

- Write protection ❐ Hardware protection using Write Protect (WP) pin ❐ Software block protection for one-quarter, one-half, or entire array 2

- I C access to special functions ❐ Nonvolatile STORE/RECALL ❐ 8 byte serial number ❐ Manufacturer ID and Product ID ❐ Sleep mode

- Low power consumption ❐ Average active current of 1 mA at 3.4 MHz operation ❐ Average standby mode current of 150 µA ❐ Sleep mode current of 8 µA ❐ ❐ Industry standard configurations ❐ Operating voltages:

- CY14C512J: VCC = 2.4 V to 2.6 V

- CY14B512J: VCC = 2.7 V to 3.6 V

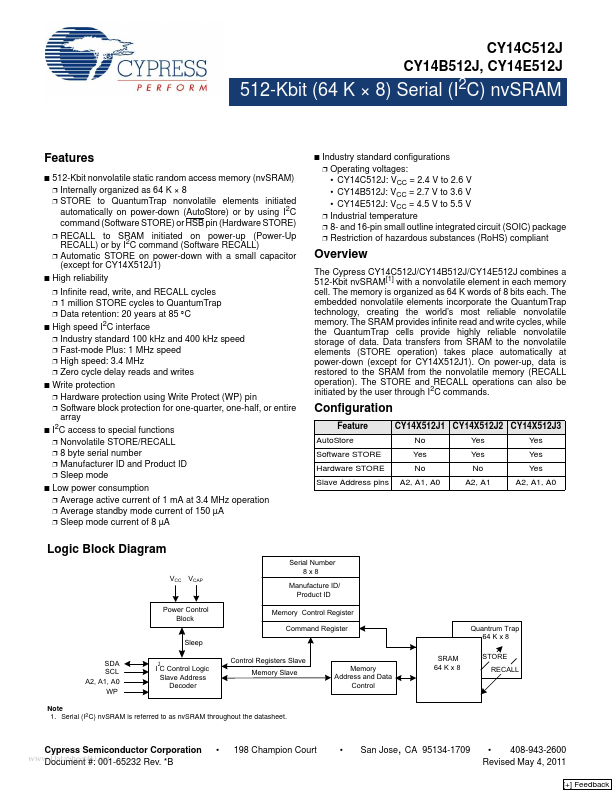

- CY14E512J: VCC = 4.5 V to 5.5 V ❐ Industrial temperature ❐ 8- and 16-pin small outline integrated circuit (SOIC) package ❐ Restriction of hazardous substances (RoHS) compliant Overview The Cypress CY14C512J/CY14B512J/CY14E512J combines a 512-Kbit nvSRAM[1] with a nonvolatile element in each memory cell. The memory is organized as 64 K words of 8 bits each. The embedded nonvolatile elements incorporate the QuantumTrap technology, creating the world’s most reliable nonvolatile memory. The SRAM provides infinite read and write cycles, while the QuantumTrap cells provide highly reliable nonvolatile storage of data. Data transfers from SRAM to the nonvolatile elements (STORE operation) takes place automatically at power-down (except for CY14X512J1). On power-up, data is restored to the SRAM from the nonvolatile memory (RECALL operation). The STORE and RECALL operations can also be initiated by the user through I2C commands. Configuration Feature AutoStore Software STORE Hardware STORE Slave Address pins CY14X512J1 CY14X512J2 CY14X512J3 No Yes No A2, A1, A0 Yes Yes No A2, A1 Yes Yes Yes A2, A1, A0 Logic Block Diagram Serial Number 8x8 VCC VCAP Manufacture ID/ Product ID Memory Control Register Command Register Sleep SDA SCL A2, A1, A0 WP 2 Power Control Block Quantrum Trap 64 K x 8 SRAM 64 K x 8 STORE RECALL Control Registers Slave Memory Slave Memory Address and Data Control I C Control Logic Slave Address Decoder Note

- Serial (I2C) nvSRAM is referred to as nvSRAM throughout the datasheet. Cypress Semiconductor Corporation Document #: 001-65232 Rev. *B