CY2077

Overview

- Sixteen selectable post-divide options, using either PLL or reference oscillator/external clock Programmable PWR_DWN or OE pin, with asynchronous or synchronous modes Low jitter outputs typically ❐ 80 ps at 3.3 V/5 V Controlled rise and fall times and output slew rate Available in both commercial and industrial temperature ranges Factory programmable device options High-accuracy PLL with 12-bit multiplier and 10-bit divider EPROM programmability 3.3 V or 5 V operation Operating frequency ❐ 390 kHz-133 MHz at 5 V ❐ 390 kHz-100 MHz at 3.3 V Reference input from either a 10-30 MHz fundamental toned crystal or a 1-75 MHz external clock EPROM selectable TTL or CMOS duty cycle levels * * * *

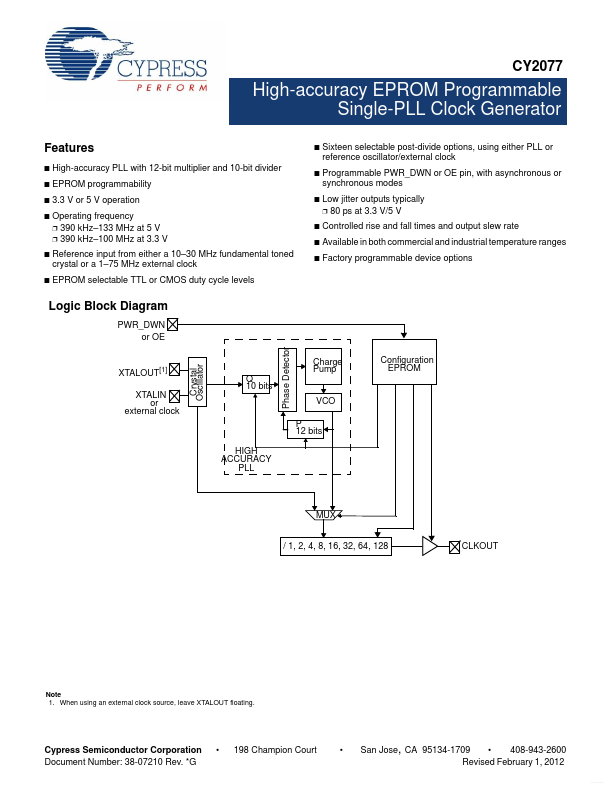

- Logic Block Diagram PWR_DWN or OE Phase Detector Crystal Oscillator Charge Pump Configuration EPROM XTALOUT[1] XTALIN or external clock Q 10 bits